5.4 PORT D :

C'est un port 8 bits bidirectionnel, la configuration de ce port

se fait à l'aide du registre TRISD. Les registres associés sont

:

|

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

|

PORTD

|

RD7

|

RD6

|

RD5

|

RD4

|

RD3

|

RD2

|

RD1

|

RD0

|

|

TRISD

|

Registre de Direction du PORTD

|

|

TRISE

|

IBF

|

OBF

|

IBOV

|

PSPMODE

|

x

|

Registre de direction

|

V' Registre TRISD :

Chaque broche est configurable en entrée ou en sortie.

Pour la configurer en entrée le TRISD doit être mis à 1,

sinon 0 en sortie.

Le PORTD peut être utilisé dans un mode

particulier appelé " parallel slave port

" pour cela il faut placer le bit 4 (PSPMODE) de

TRISE à 1. Dans ce cas les 3 bits de PORTE deviennent les entrées

de control de ce port (RE, WE et CS).

5.5 PORT E :

Le PORTE contient seulement 3 bits RE0, RE1 et RE2. Les 3 bits

sont configurables en entrée ou en sortie à l'aide du registre

TRISE.

Les 3 bits de PORTE peuvent être utilisés soit

comme E/S numériques soit comme entrées analogiques du CAN. La

configuration se fait à l'aide du registre ADCON1. Les registres

associés sont :

|

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

|

PORTE

|

X

|

X

|

x

|

x

|

x

|

RE2

|

RE1

|

RE0

|

|

TRISE

|

Registre de Direction du PORTE

|

|

ADCON1

|

ADFM

|

X

|

x

|

x

|

PCFG3

|

PCFG2

|

PCFG1

|

PCFG0

|

V' Registre TRISE :

Si TRISE est placé à 1, Les trois bits de ce

port deviennent les entrées de control du PORTD qui fonctionne en mode "

parallel slave port ".A la mise sous tension

(RESET), les 3 broches du PORTE sont configurés en entrées

analogiques.

V' Registre ADCON1 :

Ce registre sera étudié dans le chapitre concernant

le CAN.

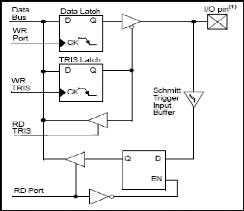

6. Module de conversion A/N :

6.1 Caractéristiques générales du

module A/D :

Le convertisseur A/D convertit le signal analogique

présent sur une de ses 8 entrées en son équivalent

numérique, codé sur 10 bits.

Les pattes AN2 et AN3 peuvent être utilisées comme

références de tension ou comme entrées analogiques

standard. Les tensions de référence haute et basse peuvent

être choisies par programmation parmi: VDD (broche PA3) pour VREF+ et VSS

(broche PA2) pour VREF- .On peut donc numériser jusqu'à 8 signaux

analogiques.

Pas tous en même temps, étant donné qu'il n'y

a qu'un seul module de conversion

pour 8 signaux d'entrées multiplexées. Mais si les

signaux n'évoluent pas trop vite (fréquence basse), la

numérisation du signal se fait sur la patte AN0, puis sur AN1...

Les paramètres importants dont il faudra tenir compte sont

:

· La résolution du convertisseur. Ici 10 bits, donc

meilleur qu'un convertisseur 8 bits, mais moins précis qu'un 12 bits.

· Le temps de conversion.

· La rapidité d'évolution des signaux

présents sur les entrées (leur fréquence pour des signaux

périodiques).

· Le nombre de signaux à numériser.

Figure I.13 : Schéma Interne du

convertisseur analogique/numérique

Registres associés avec le module

A/D

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

INTCON

|

GIE

|

PEIE

|

TOIE

|

INTE

|

RBIE

|

TOIF

|

INTF

|

RBIF

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP 1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPIE

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP 1IE

|

TMR2IE

|

TMR1IE

|

ADRESH

|

MSB du résultat du module A/D

|

ADRESL

|

LSB du résultat du module A/D

|

ADCON0

|

ADSC1

|

ADSC0

|

CHS2

|

CHS1

|

CHS0

|

GO/DONE

|

x

|

ADON

|

ADCON1

|

ADFM

|

x

|

x

|

x

|

PCFG3

|

PCFG2

|

PCFG1

|

PCFG0

|

PORTA

|

x

|

x

|

Pins D'Entrées Sorties du PORTA

|

TRISA

|

Registre de Direction du PORTA

|

PORTE

|

x

|

x

|

x

|

x

|

x

|

Pins D'Entrées Sorties du PORTE

|

TRISE

|

Registre de Direction du PORTE

|

|

y' Registre ADCON0 :

Au reset : ADCON0 = 00000000

ADSC1 ADSC0: Clock Select bits.

Ces 2 bits permettent de choisir la vitesse de conversion :

00= Fosc/2 - 01= Fosc/8 - 10= Fosc/32 - 11= Oscillateur RC

interne. CHS2 CHS1 CHS0: Channel Select bits.

Ces 3 bits permettent de choisir l'entrée qui va

être convertie.

Canal

|

CHS2

|

CHS1

|

CHS0

|

PORT

|

0

|

0

|

0

|

0

|

RA0

|

1

|

0

|

0

|

1

|

RA1

|

2

|

0

|

1

|

0

|

RA2

|

3

|

0

|

1

|

1

|

RA3

|

4

|

1

|

0

|

0

|

RA5

|

5

|

1

|

0

|

1

|

RE0

|

6

|

1

|

1

|

0

|

RE1

|

7

|

1

|

1

|

1

|

RE2

|

|

GO/DONE: 1 = Démarre la conversion A/D -

0 = La conversion A/D est terminée. ADON

: 1 = Convertisseur A/D en service - 0 =

Convertisseur A/D à l'arrêt.

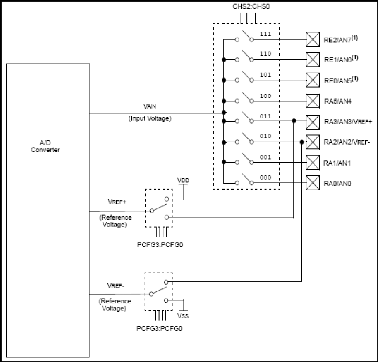

y' Registre ADCON1:

Au reset : ADCON1 = 00000000

ADFM: A/D Result format.

1= Justifié à droite. ADRESH ne

contient que les 2 MSB du résultat. Les 6 MSB de ce registre sont lus

comme des "0".

0= Justifié à gauche. ADRESL ne

contient que les 2 LSB du résultat. Les 6 LSB de ce registre sont lus

comme des "0".

Figure I.14 : Schéma de justification de

la donnée convertie

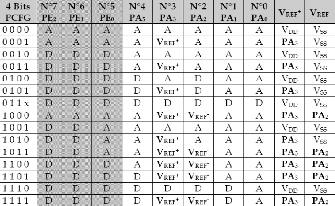

PCFG3 PCFG2 PCFG1 et PCFG0 : Bits de

contrôle de la configuration des Ports. Ces bits permettent de choisir le

partage entre entrées analogiques et digitales sur les PORTS A et E.

7. Interface série asynchrone :

L'USART: "Universal Synchronous Asynchronous Receiver

Transmitter" ou "SCI" en anglais (Serial

Communication Interface) est l'un des deux modules de

communication série du PIC. Comme son nom l'indique, il

peut établir une liaison synchrone ou asynchrone, recevoir et

transmettre des données, selon la manière dont il est

configuré.

L'USART permet de communiquer avec le reste du monde : un

ordinateur ou tout autre matériel équipé d'une interface

série RS232, des circuits intégrés convertisseurs

Numérique/Analogique ou Analogique/Numérique, des EEPROMs

série...

La communication se fait sur les deux broches RC6/TX et RC7/RX

qui doivent être configurés toutes les deux en entrée par

TRISC.

L'USART peut être configurée selon 3 modes :

· Asynchrone (Full Duplex).

· Synchrone Maître (Half Duplex).

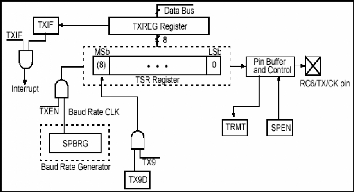

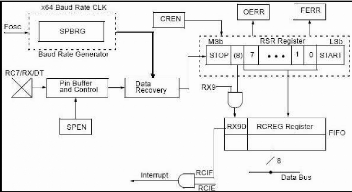

· Synchrone Esclave (Half Duplex). Figure

I.15 : Schéma interne du port en transmission

Figure I.16 : Schéma interne du port en

réception

Registres associés avec

L'USART

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

INTCON

|

GIE

|

PEIE

|

TOIE

|

INTE

|

RBIE

|

TOIF

|

INTF

|

RBIF

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPIE

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP1IE

|

TMR2IE

|

TMR1IE

|

RCSTA

|

SPEN

|

RX9

|

SREN

|

CREN

|

x

|

FERR

|

OERR

|

RX9D

|

TXREG

|

USART Transmettent Le Registre

|

TXSTA

|

CSRC

|

TX9

|

TXEN

|

SYNC

|

x

|

BRGH

|

TRMT

|

TX9D

|

SPBRG

|

Registre De Générateur De Vitesse

baud

|

|

V' Registre TXSTA : Registre d'état

Emission

Au reset : TXSTA = 00000010

CSRC : Clock Source en synchrone. (Sans

importance en asynchrone) TX9 : Autorisation d'émission

sur 9 bits. 1= Autorisé - 0 = Non

autorisé. TXEN :Autorisation d'émission.

1= Autorisé - 0 = Non

autorisé.

SYNC : Sélection mode Synchrone /

Asynchrone.

1= Mode synchrone - 0 = Mode

asynchrone.

BRGH : Sélection vitesse rapide en mode

asynchrone.

1 = Vitesse haute sélectionnée -

0 = Vitesse basse sélectionnée.

TRMT : bit d'état du registre à

décalage Emission.

1 = Registre vide, émission

terminée - 0 = Registre plein, émission en

cours. TX9D : 9eme bit de Données transmise. Ce bit

peut être le bit de la parité.

V' Le Registre RCSTA : Registre d'état

Réception

Au reset : RCSTA = 0000000x

SPEN : Serial Port Enable. PC7 et PC6

configurés pour le port série. 1 = Port

série en service - 0 = Port série

désactivé.

RX9 : Autorisation de réception sur 9

bits. 1 = Autorisé - 0 = Non

autorisé.

SREN : Single Receive Enable.

Réservé pour mode Synchrone. (Non utilisé en mode

Asynchrone)

CREN :Continous Receive Enable.

1 = Autorise la réception - 0 =

Désactive la réception. ADDEN: Adress Detect

Enable. En mode Asynchrone 9 bits:

1 = Autorise la détection d'adresse, et

charge la donnée dans le registre de réception RCREG quand le

9eme bit du registre de dé sérialisation vaut "1".

0 = Dé sélecte la

détection d'adresse. Tous les octets sont reçus et le 9eme bit

peut servir de bit de parité.

FERR :Framing Error.

1 = Une erreur de Framing est survenue -

0 = Pas d'erreur de Framing.

OERR :Overrun Error.Un octet est reçu

alors que le registre de réception n'a pas été vidé

par lecture. 1 = Erreur Overrun - 0 = Pas

d'erreur Overrun.

RX9D : 9eme bit de Data reçue, ce bit

peut être le bit de la parité.

y' Registre SPRBGH :

Le Baud Rate Generator est un registre 8 bits qui contient le

facteur de division (N) de l'horloge interne qui permet d'obtenir la vitesse

commune d'émission et de réception. BRGH=1 Vitesses haute -

BRGH=0 Vitesses basse.

I Registre TXREG : Registre

d'émission.

L'émission est autorisée par la mise à

"1" du bit TXEN. La donnée à transmettre est

mise dans le registre TXREG, TXIF = 1 le registre

prévient qu'il est vide, ce flag passe à "0" dés que l'on

charge un octet dans le registre TXREG. Il repasse à

"1" par Hard. Ce flag passe à "0" dés que l'on charge un octet

dans le registre TXREG. Il repasse à "1" par Hard quand

le registre est vidé par transfert dans le registre de

sérialisation : TSR. Ce registre n'est pas accessible

par l'utilisateur, il n'a pas d'adresse.

Le flag TXIF permet aussi de générer une

interruption, à condition qu'elle soit

autorisée par mettre TXIE = 1. Il faut dans ce cas

autoriser les interruptions des périphériques par mise à

PEIE = 1, et par poser GIE = 1. (Pout l'émission et la

réception)

I Registre RCREG: Registre Réception

L'émission est autorisée par TXEN

= 1.La donnée à transmettre est mise dans le registre

TXREG. Ce registre prévient qu'il est vide en mettant

le flag TXIF à "1". Ce flag passe à "0"

dés que l'on charge un octet dans le registre TXREG. Il

repasse à "1" par Hard quand le registre est vidé par transfert

dans le registre de sérialisation TSR.

Le bit TRMT informe sur l'état du registre TSR. Quand

le registre TSR n'a pas fini de sérialisé, TRMT=0. Ce flag

repasse à "1" quand le registre est vide, c'est à dire quand le

stop a été émis.

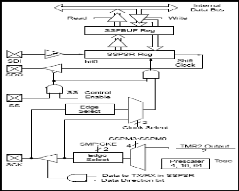

8. Module MSSP (Master Synchronous Serial Port) :

Le module SSP est la deuxième interface de communication

série du PIC.

En fait, il s'agit d'un port Maître, donc l'appellation

exacte est MSSP : « Master Synchronous Serial Port ». Il est

utile pour communiquer avec d'autres modules ou microcontrôleurs, des

EEPROMs séries, des registres à décalage, des afficheurs,

des convertisseurs A/N.

Il peut fonctionner dans deux modes de communication :

· Le mode SPI (Serial Peripheral Interface).

· Le mode I2C (Inter-Integrated Circuit).

L'utilisation de l'un de ces deux modules de communication,

USART ou MSSP dépend donc essentiellement du protocole de communication

nécessaire.

Schématiquement, l'USART est bien adaptée pour

communiquer avec le reste de l'univers via la célèbre interface

RS232 alors que le MSSP permet de communiquer aisément avec d'autres

composants électroniques à interface série.

Figure I.17 : Schéma interne du module

MSSP en mode SPI

Registres associés avec Le MSSP en mode

SPI

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

INTCON

|

GIE

|

PEIE

|

TOIE

|

INTE

|

RBIE

|

TOIF

|

INTF

|

RBIF

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPIE

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP1IE

|

TMR2IE

|

TMR1IE

|

SSPBUF

|

Le Port série Synchrone Reçoivent buffer

/ Transmettre Le Registre

|

SSPCON

|

WCOL

|

SSPOV

|

SSPEN

|

CKP

|

SSPM3

|

SSPM2

|

SSPM1

|

SSPM0

|

SSPSTAT

|

SMP

|

CKE

|

D/A

|

P

|

S

|

R/W

|

UA

|

BF

|

|

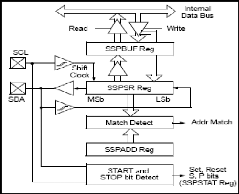

Figure I.18 : Schéma interne du module

MSSP en mode I2C

Registres associés avec Le MSSP en mode I2C

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

INTCON

|

GIE

|

PEIE

|

TOIE

|

INTE

|

RBIE

|

TOIF

|

INTF

|

RBIF

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP 1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPIE

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP1IE

|

TMR2IE

|

TMR1IE

|

PIR2

|

X

|

(2)

|

x

|

EEIF

|

BCLIF

|

x

|

x

|

CCP2IF

|

PIE2

|

X

|

(2)

|

x

|

EEIE

|

BCLIE

|

x

|

x

|

CCP2IE

|

SSPBUF

|

Le Port série Synchrone Reçoivent buffer

/ Transmettre Le Registre

|

SSPCON

|

WCOL

|

SSPOV

|

SSPEN

|

CKP

|

SSPM3

|

SSPM2

|

SSPM1

|

SSPM0

|

SSPCON2

|

GCEN

|

ACKSTAT

|

ACKDT

|

ACKEN

|

RCEN

|

PEN

|

RSEN

|

SEN

|

SSPADD

|

Adresse D'Esclave d'I2C/ / Registre Maitre De Vitesse

baud

|

SSPSTAT

|

SMP

|

CKE

|

D/A

|

P

|

S

|

R/W

|

UA

|

BF

|

|

V' Registre SSPSTAT : registre d'état Au

reset : SSPSTAT = 00000000

SMP : bit d'échantillonnage.

CKE : Clock Edge Select. Ce bit à "0" :

conforme aux spécifications I2C.

D/A: Data / Adresse bit.

1 = indique que le dernier octet reçu

est une donnée

0 = indique que le dernier octet reçu

est une adresse.

P : STOP bit. Ce bit est remis à "0"

quand le module SSP est désactivé.

1 = un Stop a été

détecté. - 0 = il n'a pas détecté

le Stop.

S : START bit. Ce bit est remis à "0"

quand le module SSP est désactivé.

1 = un Start a été

détecté. - 0 = il n'a pas été

détecté de Start.

R/W : Information sur le bit R/W. Donne la

valeur de ce bit qui suit la dernière adresse. Ce

bit est valable jusqu'à la réception du STOP.

Mode ESCLAVE : 1 = R - 0 = W. Mode

MAITRE : 1 = Transmission en cours - 0 = Pas de

transmission en cours.

UA : mise à jour adresse. Utilisé

en mode 10 bits seulement.

BF : Buffer plein.

Mode Réception I2C:

Registre plein =1 : réception terminée - Registre

vide= 0: donc réception non

terminée.

Mode Emission I2C:

Registre plein =1: donc émission en

cours. Registre vide= 0 : donc émission

terminée.

V' Registre SSPCON : registre de

contrôle

Au reset : SSPCON = 00000000

WCOL : détection de collision à

l'écriture.

1 = Collision à l'écriture. - 0 = Pas de

collision.

SSPOV : Overflow indicator en

réception.Doit être remis à "0" par soft

1 = Un octet vient d'être reçu dans le buffer:

Overflow.- 0 = Pas d'Overflow.

SSPEN : Enable Module SSP.

1 = Module I2C activé et pin SCL et SDA sur PC3 et PC4

configurées. 0 = Module I2C désactivé. PC3 et PC4 libres

pour usage I/O.

CKP : Polarité du Clock.

Inutilisé en mode maître.

Mode Esclave : 1 = Autorise horloge. - 0 =

Maintient CLK = 0.

SSPM3, SSPM2, SSPM1et SSPM0 : Select Mode.

SSPM3

|

SSPM2

|

SSPM1

|

SSPM0

|

MODE

|

0

|

1

|

1

|

0

|

I2C esclave 7 bits

|

0

|

1

|

1

|

1

|

I2C esclave 10 bits

|

1

|

0

|

0

|

0

|

I2C maitre CLK =Fosj4(sspadd+1)

|

|

I Registre SSPCON2 : registre de contrôle

n°2.

Au reset : SSPCON2 = 00000000

GCEN : Appel général en mode I2C

esclave seulement.

1 = Autorise IT quand une adresse appel général

(h'0000) est reçue.

0 = Adresse appel général

désactivée.

ACKSTAT : Bit d'ACK en mode I2C maître

seulement.

1 = Pas de ACK reçu de l'esclave - 0 = ACK de l'esclave a

été reçu.

ACKDT : ACK Data bit. En mode maître et

réception : valeur qui sera transmise quand on va lancer une

séquence de ACK en fin de réception.

1 = NO ACK - 0 = ACK.

ACKEN: ACK Sequence Enable. En mode

maître et réception, lance une séquence d'ACK ou de NOACK

suivant la valeur dans ACKDT.

1 = Lance la séquence de ACK et transmet ACKDT. Remis

à "0" par hard. 0 = Pas de séquence d'ACK.

RCEN : Receive Enable Bit. En mode I2C

maître seulement.

1 = Autorise mode réception- 0 = Pas de réception

autorisée.

PEN : Stop Condition Enable. En mode I2C

maître seulement.

1 = Lance la séquence de STOP sur SDA et SCL. Remis

à "0" par hard

0= Pas de séquence de STOP

RSEN : Repeated Start Condition. En mode I2C

maître seulement.

1 = Séquence de répétition de START sur SDA

et SCL. Remis à "0" par hard. 0 = Pas de séquence de

répétition de START.

SEN = Start Condition Enable. En mode I2C

maître seulement.

1 = Lance la séquence de START sur SDA et SCL. Remis

à "0" par hard. 0 = Pas de séquence de START.

MODE MAITRE :

Les pins SDA et SCL sont manipulées par le Hard. Les

événements qui causent le passage à "1" du flag S SPIF et

éventuellement une si elles sont autorisées, sont :

- Condition de START.- Condition de STOP.-

Répétition d'un START. - ACK après un

transfert et Transfert d'octet en Emission ou réception.

(Le flag SSPIF doit être remis à "0" par soft).

Lancement d'un START:

L'utilisateur doit mettre le bit SEN "1". Les pins SDA et SCL

étant toutes les deux à "1 ", le module fait passer la pin SDA de

"1" à "0" ce qui génère une condition de START.

Le bit S passe à "1" pour signaler le START. A la fin du

START, le bit SEN est remis à "0" par le hard. Dés que le flag

SSPIF passe à "1" pour signaler la fin du START, on peut charger le

registre de transmission SSBUF avec l'octet à transmettre. (Ne pas

oublier de remettre ce flag à "0"par le soft).

Transmission :

Dés que le registre SSBUF est chargé, BF passe

à "1" pour signaler que la transmission est en cours. Au 8eme coup de

CLK, la transmission est terminée et le BF repasse à "0".

Acquittement :

Quand l'esclave répond l'ACK, le bit ACKSTAT passe

à "0". La fin de l'ACK est signalée par le Flag SSPIF qui passe

à "1". On doit alors remettre ce flag à "0"par soft.

Lancement d'un STOP :

L'utilisateur doit mettre PEN à "1 ". Le module fait

alors passer SDA à "0" puis force

SCL à"1 ". Quand SCL est à "1" il fait passer SDA

de "0" à"1 ", ce qui génère une condition de STOP. P passe

à "1" pour signaler le STOP. A la fin du STOP, PEN est remis à

"0" par le hard.- Le flag SSPIF passe à "1" pour signaler la fin du

STOP.

Réponse du maître à l'esclave

:

Il s'agit soit d'un ACK soit d'un NOACK :

Positionner le bit ACKDT en fonction de la réponse

à faire. Mettre le bit ACKEN à "1". La

fin de transmission du ACK ou du non ACK est signalé par

le flag SSPIF qui passe à "1". (Ne pas oublier de le remettre à

"0" par soft)

Réception d'un octet par le maître

:

Pour cela il faut mettre le module en réception en

portant RCEN à "1 ". La fin de réception est signalée par

le passage à "1" du flag SSPIF, que l'on remettra à "0" par soft.

On peut alors lire l'octet reçu dans SSBUF.

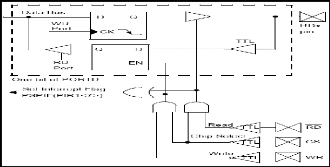

9. Port Parallèle Esclave (PSP : Parallel

Slave Port) :

Le Port Parallèle Esclave est un port 8 bits permettant

d'interfacer le PIC avec, par exemple, un autre microprocesseur. Les

données transitent via les lignes PSP0 à PSP7, qui

physiquement utilisent les mêmes broches que le PORTD. Le

flux de données est contrôlé par les lignes RD, WR et CS

qui correspondent aux broches du PORTE.C'est le microprocesseur externe qui est

le chef d'orchestre : il valide le PIC par la ligne CS (Chip Select), et

indique au PIC s'il lit ou écrivent grâce aux lignes RD (Read) et

WR (Write). D'où l'appellation de port parallèle esclave.

Esclave, puisque c'est le microprocesseur externe qui donne les ordres, le PIC

ne fait qu'exécuter.

Figure I.19 : Schéma interne du module

PSP

Registres associés avec le

PSP

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

PORTD

|

Verrou de données gauches une fois écrit

: Goupilles gauches une fois lu

|

PORTE

|

x

|

x

|

x

|

x

|

x

|

RE2

|

RE1

|

RE0

|

TRISE

|

IBF

|

OBF

|

IBOV

|

PSPMODE

|

x

|

PORTE Data Direction Bits

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPIE

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP1IE

|

TMR2IE

|

TMR1IE

|

ADCON1

|

ADFM

|

x

|

x

|

x

|

PCFG3

|

PCFG2

|

PCFG1

|

PCFG0

|

|

PSPIE = Parallel Slave Port Interrup Enable

bit.

1= Autorise les interruptions R/W du port SSP.- 0=

Désactive toutes ces interruptions. PSPIF = Parallel

Slave Port Interrup Flag bit.

1 = Une opération de R/W vient d'avoir lieu sur le port

SSP.

0 =Il n'y a pas eu de R/W sur le port SSP.

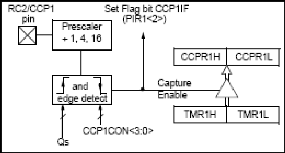

10. Modules CCP1 et CCP2 :

Ces deux modules sont identiques et composés chacun d'un

registre à 16 bits. Ils peuvent fonctionner dans l'un des trois modes

ci-dessous :

Mode capture (CAPTURE) : Ce mode permet d'effectuer des mesures

de temps.

Mode comparaison (COMPARE) : Ce mode permet de

générer des événements périodiques.

Mode PWM (PULSE WITH MODULATION): Ce mode permet de

générer des signaux dont le rapport cyclique est variable.

Ces modules sont associés aux broches R/CCP1 et

RC1/T1OSI/CCP2.

Suivant le mode choisit, les Timer1 ou Timer2 vont être

utilisés. Le mode Capture et le mode Comparaison utilise le Timer 1,

tandis que le mode PWM utilise le Timer2.

Figure I.20 : Schéma interne du module

CCP

Registres associés avec Le CCP1 et

CCP2

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

INTCON

|

GIE

|

PEIE

|

TOIE

|

INTE

|

RBIE

|

TOIF

|

INTF

|

RBIF

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPIE

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP1IE

|

TMR2IE

|

TMR1IE

|

PIR2

|

x

|

(2)

|

x

|

EEIF

|

BCLIF

|

x

|

x

|

CCP2IF

|

PIE2

|

x

|

(2)

|

x

|

EEIE

|

BCLIE

|

x

|

x

|

CCP2IE

|

TRISC

|

Registre de Direction Du PORTC

|

T MR1L

|

En tenant l'inscription au moindre byte significatif du

TMR1 de 16 bit enregistrés

|

TMR1H

|

En tenant l'inscription au byte le plus significatif du

TMR1 de 16 bits enregistré

|

SSPSTAT

|

SMP

|

CKE

|

D/A

|

P

|

S

|

R/W

|

UA

|

BF

|

T1CON

|

x

|

x

|

T1CKPS1

|

T1CKPS0

|

T1OSCEN

|

T1SYNC

|

TMR1CS

|

TMR1ON

|

CCPR1L

|

Capture/Compare/PWM Register1 (LSB)

|

CCPR1H

|

Capture/Compare/PWM Register1 (MSB)

|

CCP1CON

|

x

|

x

|

CCP1X

|

CCP1Y

|

CCP1M3

|

CCP1M2

|

CCP1M1

|

CCP1M0

|

CCPR2L

|

Capture/Compare/PWM Register2 (LSB)

|

CCPR2H

|

Capture/Compare/PWM Register2 (MSB)

|

CCP2CON

|

x

|

x

|

CCP2X

|

CCP2Y

|

CCP2M3

|

CCP2M2

|

CCP2M1

|

CCP2M0

|

|

y' Registre CCP1CON :

Au reset : CCP1CON = 00000000

CCP1X et CCP1Y : Bits non utilisés en

modes Compare et Capture, ce sont les 2 bits LSB pour le Duty cycle en mode

PWM. Les 8 bits MSB sont dans le registre CCPR1L. CCP1M3 à

CCP1M0 : bits de sélection du mode.

0 0 0 0 = Module CCP stoppé.

0 1 0 0 = Mode Capture à chaque front descendant.

0 1 0 1 = Mode Capture à chaque front montant.

0 1 1 0 = Mode Capture tous les 4 fronts montants.

0 1 1 1 = Mode Capture tous les 16 fronts montants.

1 0 0 0 = Mode Compare. Pin de sortie mise à "1" et Flag

CCP 1IF = 1 à l'égalité. 1 0 0 1 = Mode Compare. Pin de

sortie mise à "0" et Flag CCP 1IF = 1 à

l'égalité.

1 0 1 0 = Mode Compare. Génération d'une

Interruption et Flag CCP1IF = 1 à l'égalité. 1 0 1 1 =

Mode Compare. Evénement spécial généré et

Flag CCP1IF = 1 à l'égalité.

1 1 x x = Mode PWM.

MODE COMPARE :

Les deux modules CCP étant identiques on ne

décrira que le module 1. Les 16 bits des registres CCPR1 (CCPR1H et

CCPR1L) sont constamment comparés avec le valeur sur 16 bits des

registres du Timer 1 (TMR1H et TMR1L). Quand il y a égalité, la

broche préalablement programmée en sortie P, passe soit à

"1" soit à "0" suivant la configuration des 4 bits CCP1M du registre

CCP1CON. Au même instant le Flag CCP1IF est mis à "1".

En mode Compare, les événements spéciaux

générés quand il y a égalité sont: - Pour

CCP1: reset du Timer 1.

- Pour CCP2 : reset du Timer 1 et démarrage d'une

conversion A/D.

Dans ce cas la broche de sortie n'est pas affectée, mais

le Flag CCP 1IF est mis à " 1". Il est rappelé que ce Flag doit

être remis à "0" par soft.

MODE CAPTURE :

Quand un événement extérieur

apparaît sur la broche préalablement programmée en

entrée P, la valeur des 16 bit des registres du Timer 1 (TMR1L et TMR1H)

est recopiée dans les registres CCPR1 (CCPRIH et CCPR1L). Cet

événement est programmable par les 4 bits CCP1M du registre

CCP1CON. La capture peut avoir lieu à chaque front descendant, à

chaque front montant, tous les 4 ou tous les 16 fronts montants. Quand la

capture a eu lieu, le flag CCP1IF est mis à "1". Ce bit doit être

remis à "0" par soft. Les fonctions de Capture et de Compare sur le

Timer 1 par les modules CCP1 et CCP2 peuvent générer une

interruption quand le Flag CCP1IF passe à "1" si le bit d'autorisation

CCP1IE du registre PIE1 est mis à "1".

MODE PWM :

Un signal PWM est caractérisé par une

période, et un temps de travail ou le signal est à "1 ". Ce temps

est appelé DUTY CYCLE. La broche P doit être configurée

comme une sortie en mettant le bit 2 de TRISC à "0".

Le signal PWM est fabriqué à partir du Timer 2. Le

signal interne Fosc/4 passe à travers le pré diviseur

programmable par 1, 4 ou 16 et fait compter TMR2.Quand ce registre atteint la

valeur écrite dans le registre PR2, trois événements se

produisent :

- RAZ du registre TMR2.

- La broche de sortie P est mise à "1 ", sauf si le Duty

cycle vaut 0.

- Chargement de la valeur du registre CCPR1L dans le registre de

Duty.

Quand le registre TMR2 atteint la valeur inscrite dans le

registre interne de Duty, c'est à dire la valeur qui avait

été inscrite dans CCPR1L, la broche de sortie P est remise

à "0". La période est déterminée par la relation

suivante :

T = [PR + 1]* 4 * T * valeur du

pré diviseur

La durée du Duty cycle est la valeur écrite dans

le registre 8 bits : CCPR1 L. La durée du signal au niveau "1" est

donnée par la relation :

D = [CCPR1L]* 4 * T * valeur

du pré diviseur

On peut avoir une meilleure r ésolution sur le Duty cycle

en utilisant les 2 bits de LSB réservés à cet effet dans

le registre CCP1CON.

Il s'agit de CCP1X et CCP1Y. La résolution est dans ce

cas divisée par 4. Si on appelle X le registre sur 10 bits,

constitué de ces 2 bits en LSB et des 8 bits de CCPR1L comme MSB, la

durée à "1" est donnée par la relation :

D = X * Tosc * valeur du pré

diviseur

Dans les 2 cas, quand on incrémente le registre CCPR1L de

une unité, le Duty cycle augmente d'une durée égale

à : 4.Tosc.valeur du pré diviseur.

Quand on passe à "1" le bit 5 la durée augmente de

2 x Tosc x pré div.

Quand on passe à "1" le bit 4 de CCP1CON, la durée

augmente de Tosc.pré div Si la durée du Duty cycle est

supérieure à la période, le signal n'est pas remis

à "0".

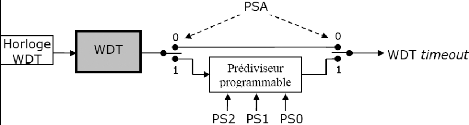

11. Timers :

Le PIC 16F877 dispose de 3 timers :

· Timer 0 (8 bits): Il peut être

incrémenté par des impulsions extérieures via la broche

(TOCKI/ RA4) ou par l'horloge interne (Fosc/4).

· Timer 1 (16 bits): Il peut être

incrémenté soit par l'horloge interne, ou soit par des impulsions

sur la broche T1CKI/RC0 ou par un oscillateur (RC ou quartz) connecté

sur les broches TOSO/RCO et T1OSI/RC1.

· Timer 2 (8 bits) : Il est

incrémenté par l'horloge interne, celle peut être

prédivisée. Tous ces timers peuvent déclencher une

interruption interne, s'ils ont été autorisés.

11.1 Timer0 :

C'est le plus ancien des timers implantés dans les PICs,

son ancienne appellation était

RTC, pour Real Time Clock (horloge temps réelle). On peut

se servir de celui-ci pour générer des événements

périodiques, comme le rafraîchissement d'afficheurs

multiplexés ou l'incrémentation de variables (secondes, minutes

...).

Registres associés avec Le

TMR0

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

TMR0

|

Registre compteur

|

INTCON

|

GIE

|

PEIE

|

T0IE

|

INTE

|

RBIE

|

T0IF

|

INTF

|

RBIF

|

OPTION_REG

|

RBPU

|

INTEDG

|

T0CS

|

T0SE

|

PSA

|

PS2

|

PS1

|

PS0

|

|

y' Registre OPTION : Au reset : OPTION =

11111111 TOCS: Timer TMR0 Clock Source select bit.

1 = L'horloge du Timer est l'entrée

PA4/Clk (pin 3).

0 = Le Timer utilise l'horloge interne du

PIC.

TOSE: Timer TMR0 Source Edge select bit.

1 = Le Timer s'incrémente à

chaque front montant de la broche PA4/Clk.

0 = Le Timer s'incrémente à chaque

front descendant de la broche PA4/Clk.

PSA : Prescaler Assignement bit.

1 = Le prédiviseur est affecté au

watchdog. - 0 = Le prédiviseur est affecté au

Timer

PS2 PS1 PS0: Prescaler Rate Select bits.

PS2

|

PS1

|

PS0

|

Prédiv Timer

|

Prédiv Watchdog

|

0

|

0

|

0

|

2

|

1

|

0

|

0

|

1

|

4

|

2

|

0

|

1

|

0

|

8

|

4

|

0

|

1

|

1

|

16

|

8

|

1

|

0

|

0

|

32

|

16

|

1

|

0

|

1

|

64

|

32

|

1

|

1

|

0

|

128

|

128

|

1

|

1

|

1

|

256

|

256

|

|

Figure I.21 : Schéma interne

simplifié du TMR0 sans le WA TCHDOG

11.2 Le Timer1 :

Le Timer1 fonctionne sur le même principe que le

Timer0, mais avec un registre de

comptage plus gros : 16 bits au lieu de 8, ce qui étend

notablement ces capacités de comptage. Il est accessible en

lecture/écriture par l'intermédiaire des registres 8 bits TMR1H

et TMR1L, On le configure à l'aide du registre T1CON. On peut l'utiliser

en association avec un des modules CCP (modules de capture et

de comparaison)

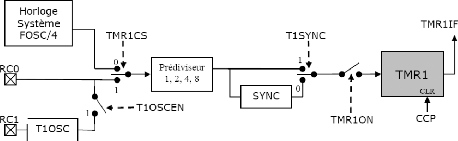

Figure I.22 : Schéma interne du

TMR1

Registres associés avec Le TMR1

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

INTCON

|

GIE

|

PEIE

|

T0IE

|

INTE

|

RBIE

|

T0IF

|

INTF

|

RBIF

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPI

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP1IE

|

TMR2IE

|

TMR1IE

|

TMR1L

|

Registre compteur ( 8bits) poids faible

|

TMR1H

|

Registre compteur (8 bits) pois fort

|

T1CON

|

x

|

x

|

T1CKPS1

|

T1CKPS0

|

T1OSCEN

|

T1SYNC

|

TMR1CS

|

TMR1ON

|

|

V' Le registre T1CON : Sélection du

pré diviseur placé avant le TIMER.

Au reset : T1CON = 00000000

T1CKPS1 T1CKPS0 : Bits Sélection du

pré diviseur placé avant le TIMER.

00 = Prédiviseur 1.

01 = Prédiviseur 2.

10 = Prédiviseur 4.

11 = Prédiviseur 8.

T1OSCEN : Bit d'autorisation de l'oscillateur

du Timer 1.

1 = oscillateur autorisé -0 = oscillateur

stoppé.

T1SYNC : Bit de contrôle de la

synchronisation du CLK externe.

1 = Pas de synchronisation de l'horloge externe. 0 =

Synchronisation de l'horloge

externe.

TMR1CS : Bit de sélection de la source

horloge.

1 = Mode Compteur: Clk externe sur la broche PC0 ou Quartz

entre PC0 et PC 1

0 = Mode Timer: Clk interne = Fosc/4.

TMR1ON : Bit d'autorisation du Timer 1.

1= Timer 1 en service. -0 = Timer 1 stoppé.

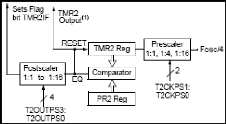

11.3 Le TIMER2 :

Le Timer2 a un fonctionnement différent des Timer0 et

Timer 1. C'est un compteur 8 bits avec prédiviseur et postdiviseur. Son

horloge ne peut être que l'horloge interne divisée

par 4 (Fosc/4).On s'en sert pour générer des

signaux carrés, ou, en association avec le module CCP, des signaux

PWM.

Figure I.23 : Schéma du

TMR2

Registres associés avec Le Timer2

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

INTCON

|

GIE

|

PEIE

|

T0IE

|

INTE

|

RBIE

|

T0IF

|

INTF

|

RBIF

|

PIR1

|

PSPIF

|

ADIF

|

RCIF

|

TXIF

|

SSPIF

|

CCP 1IF

|

TMR2IF

|

TMR1IF

|

PIE1

|

PSPI

|

ADIE

|

RCIE

|

TXIE

|

SSPIE

|

CCP1IE

|

TMR2IE

|

TMR1IE

|

TMR2

|

Registre compteur

|

T2CON

|

x

|

TOUTPS3

|

TOUTPS2

|

TOUTPS1

|

TOUTPS0

|

TMR2ON

|

T2CKPS1

|

T2CKPS0

|

|

V' Registre T2CON :

TOUTPS : Programmation du Post diviseur.

0 0 0 0 = post divise par 1. 0 0 0 1 = post

divise par 2. 0 0 1 0 = post divise par 3. . . . .

1 1 1 1 = post divise par 16.

TMR2ON : mise en service du Timer 2.

1= Timer 2 On.6- 0= Timer 2 Off.

T2CKPS : Programmation du pré

diviseur.

0 0= pré divise par 1.

0 1= pré divise par

4.

X= pré divise par 16.

TMR2IE : TMR2 Interrup Enable bit.

1= Autorise les interruptions du Timer 2 TMR2. - 0 =

Désactive cette interruption.

TMR2IF: TMR2 Interrup Flag bit.

1 = Le Timer2 a fait une IT. - 0 = Pas d'IT du TIMER 2.

12. Les interruptions :

Le microcontrôleur dispose de 14 sources d'interruptions

:

· Une interruption externe, action sur la broche

INT/RB0.

· Débordement du Timer0.

· Changement d'état logique sur une des broches du

PORTB (RB4 à RB7).

· Fin de programmation d'une case mémoire de

l'EEPROM.

· Changement d'état sur le PORTD

· Fin de conversion analogique numérique

· Réception d'une information sur la liaison

série

· Fin d'émission d'une information sur la liaison

série

· Interruption SPI ou I2C du module MSSP

· interruption du registre de capture et/ou de comparaison

1

· Interruption du registre de capture et/ou de comparaison

2

· Débordement du Timer 1

· Débordement du Timer2

Une demande d'interruption ne peut aboutir au processeur que

si tous les bits d'autorisation

qui se trouvent sur son chemin sont activés.

Exécution

En cours

|

|

Save PC

0 GIE

|

|

Execution retour

SPI

|

|

Reprise exécution

Suspendue

|

|

V' Fonctionnement :

- Le proceseur est en cour d'exécution (un programme ou

un sous programme). - Un evenemment=> arrive FLAG mis à 1

=>demmande d'intruption :

Si les bits d'otorisation sont validées le processeur

répond.

- Le processeur sauvegarde le PC dans la pile et mis à 0

le bit de contrôle GIE .ce ci à fin d'éviter que le CPU ait

éventuellement intérempu pendant l'éxécution du

SPI.

- Le processeur se branche vers la routine SPI et

l'éxécute ,cette rroutine doit étre à l'adress

0x0004.

- Le SPI se termine par l'instruction de retour,

l'exécution de cette instruction consiste à remettre à 1

le bit GIE puis à récupérer et mètre dans le PC

l'adresse de retour.

- Le processeur reprend l'exécution suspendue.

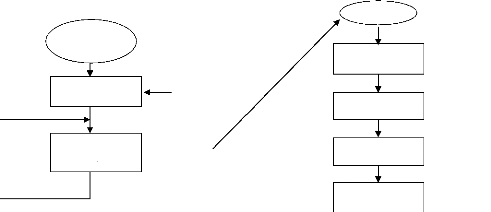

- On peut schématiser les interruptions sur les PIC par

l'organigramme suivant :

Instruction

quelleconque

Sauvegarder

l'événement

Evénement déclencheur

Instruction xxx

(1/2cycle)

Détecter quel

événement

est

survenu

Organigramme

principal

Sous programme

d'interruption

Programme

principal

Sous programme

d'interruption

Traiter l'événement

Restaurer

l'événement

Return

Instruction suivante

Suite de Programme

Événement

Implémentation d'une fonction sous interruption

:

SPI

Autorisation D'interruption

Sous programme

d'interruption

Programme

principal

Initialisation

principale

Boucle principale

BP

Sauvegarde

contexte

RAZ flag

Traitement

Restitution contexte

Return

Cas de plusieurs sources d'interruption:

Restitution contexte

Return

RAZ flag

RAZ flag

SPI

Sauvegarde

contexte

FLAG=1

FLAG=1

Traitement 1

Traitement 1

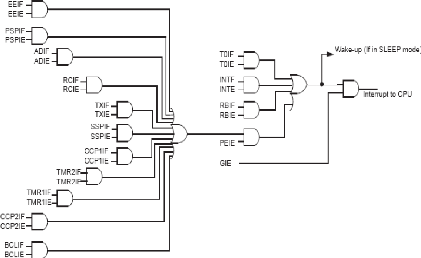

Figure I.24 : Schéma interne des

interruptions

rtie Pratiq

|

|

Applications du PIC 16F8

|

|

|

:

Présentation de la Carte

EASYPI

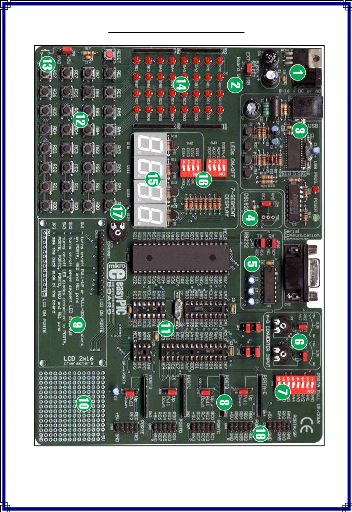

Ce starter-kit "EASYPI" est spécialement conçu

pour supporter les microcontrôleurs 18, 28 et 40 broches de la famille

PIC 16F87x. Une nouvelle version existe avec

programmateur USB intégré.

Le starter-kit "EASYPIC " permet ainsi de tester,

d'étudier et de communiquer avec la plupart des

périphériques qui peuvent être rencontrer dans les

applications industrielles:

· Afficheurs LCD ou 7 segments.

· Claviers de saisie.

· Affichage par Led.

· communication série.

· Mesure et contrôle de température.

· Conversion analogique / numérique.

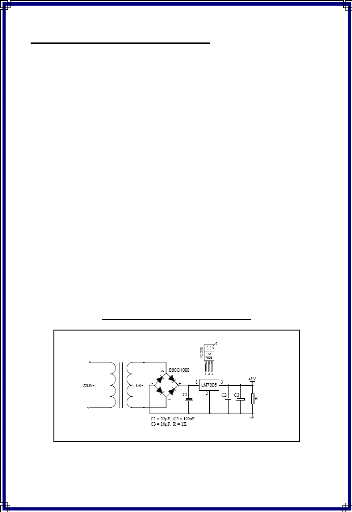

L'alimentation externe du PIC :

Il est exigé pour tous les éléments dans

le système de développement d'avoir +5V stabilisé. Le

système EasyPI utilise le régulateur de tension LM7805. En outre,

l'alimentation d'énergie d'USB peut être utilisée qui

permet à EasyPI de fonctionner sans alimentation d'énergie

externe.

Figure II.1 : Schéma interne de

l'alimentation

38

Figure II.2 : Photo de la carte EASY

PI

Dans la partie pratique on a étudié les

différentes interfaces du pic 1 6F877 telle que : le port

parallèle, le port série, le convertisseur ...

Dans chaque interface on a cité plusieurs exemples

d'applications avec leurs schémas et leurs organigrammes.

Mais par manque de temps on n'a pas pu utiliser d'autres

interfaces telles que le port parallèle slave, Module MSSP, I2C, Module

de comparaison CCP1 et CCP2....

La directive CONFIG :

Cette directive contient les fameux « fusibles » qui

fixent le fonctionnement du PIC. Les valeurs écrites seront

intégrées dans le fichier « .hex » pour signaler au

programmateur les valeurs à encoder aux adresses spécifiques du

PIC.

Cette directive est programmée lors de la programmation du

PIC dans un registre

spécial, situé en mémoire programme à

l'adresse 0x2007, et ne peut plus être modifié en cours

d'exécution du programme.

Cette directive est un registre de 14 bits dont chaque bit a une

fonction précise :

- CP1/CP0 : bits 13/12 - 5/4 : Détermine

quelle zone du PIC sera protégée contre la lecture. -

DEBUG : bit 11 : Debuggage sur circuit. Permet de réserver RB7

et RB6 à la

communication avec un debugger.

- Bit 10 : non implémenté.

- WRT : bit 9 : Autorisation d'écriture

en flash.

- CPD : bit 8 : Protection en lecture de la

mémoire eeprom.

- LVP : bit 7 : Utilisation de la pin RB3/PGM

comme broche de programmation.

- BODE N : bit 6 : provoque le reset du PIC en

cas de chute de tension (surveillance de la tension d'alimentation).

- PWRTE : bit 3 : Délai de

démarrage à la mise en service. Attention, est automatiquement

mis en service si le bit BODEN est positionné.

- WDTE : bit 2 : Watchdog timer.

- FOSC1/FOSC0 : bits 1/0 : sélection du

type d'oscillateur.

Dans nos application on utilisés la configuration

suivante : pragma config | = 0x 3a71,

C'est-à-dire: CP1/CP0= OFF, WDT= OFF, PWRTE=ON,

BODEN= ON, LVP= OFF, CPD=OFF, WRT=OFF, DEBUD= OFF, FOSC1/FO=XT.

Les valeurs données sont définies dans le fichier 1

6f877.inc qui représente les équivalences pour le PIC.

|