III.2.3 Filtre FIR du 3ème ordre :

a) Structure

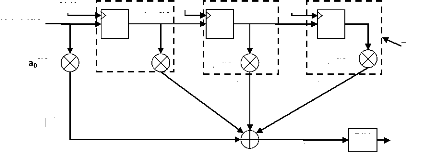

Le bloc diagramme suivant représente le principe du filtre

FIR 3éme ordres

X_in(n)[k]

[k]

[2*k]

CLK

a1[k]

Reg_1[2*k]

x-int1[k]

CLK CLK

Reg_2[2*k]

a2[k]

X_int2[k]

Reg_y[2*k+2]

Reg_3[2*k]

a3[k]

DIV

Y_out [k]

Process

Figure III.9 : bloc digramme d'un filtre FIR

3ème ordre

Nous avons utilisé la même procédure pour

créer ce filtre que celle exploité dans les deux premiers

filtres, nous avons utilisé un autre process pour créer le

troisième étage.

b) Simulation et Interprétation :

Dans cette partie nous avons utilisé une autre

méthode de test et de simulation, pour ainsi valider notre

conception.

Nous avons choisi de réaliser la simulation de ce

filtre sur logiciel Modelsim avec une entré de type x(n)= cos (n) ou la

résolution sera de 8 bits, nous avons besoin dans ce cas de figure de

crée un testbench (banc de test) pour accomplir la simulation.

Par définition, un testbench VHDL est un code VHDL

destiné à la vérification, par simulation, du bon

fonctionnement d'un système, lui-même décrit en VHDL.

Dans notre testbenchs il faut intégrés un

générateur d'horloge pour la synchronisation de ces

différents composants avec le filtre qu'on veut tester. Les coefficients

du filtre seront fixés dans le code du testbench.

L'élément le plus important est le générateur de

cosinus, il est basé sur une table de 256 valeurs qui représente

un quart de période du cosinus.

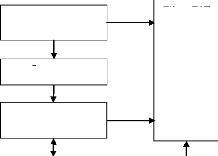

Filtre RIF

Générateur d'horloge

(CLK)

Générateur de signal

périodique

Compteur

|

ROM

(Cosinus)

|

|

ROM

Coefficients

|

|

|

Figure III.10 : Bloc diagramme du testbench avec

cosinus d'un filtre RIF

Pour générer le cosinus, il suffit de lire cette

table via un générateur d'adresse sous forme d'un compteur

cadencé par l'horloge. Pour réaliser une période de

cosinus en adresse la table 4 fois avec 4 manières différentes

:

1-

|

x_in cosrom (cont);

|

Si

|

(cont >= 0) and (cont< 257)

|

2-

|

|

x_in <= -cosrom(512-cont

|

Si

|

(cont >= 257) and (cont < 513

|

|

3-

|

x_in <= cosrom(cont-512

|

Si

|

(cont >= 513) and (cont < 769)

|

4-

|

|

xin <= cosrom(1024-cont)

|

Si

|

(cont >=769) and (cont<1024)

|

|

Pour régler la fréquence du cosinus il suffit de

changer le pas du compteur, la fréquence la plus petite équivaut

à un pas de comptage de 1. Pour une fréquence plus grande on peut

lire la table de cosinus avec un pas de 50, soit 5 valeurs

générées par 1/4 de période.

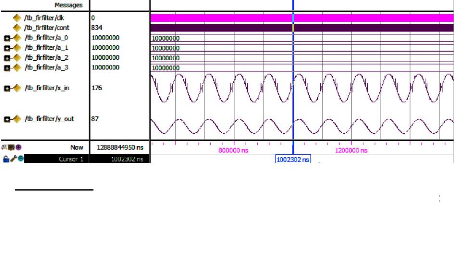

1ère simulation

Avec les paramètres suivants nous avons les

résultats de simulation de la figure III.11 :

· Horloge : 1000ns

· Largeur des données : 8 bits

· Pas de comptage : +10

Soit un cosinus d'une fréquence de 10kHz

Figure III.11 : Résultats de la

simulation d'un filtre du 3ème ordre avec f=10khz

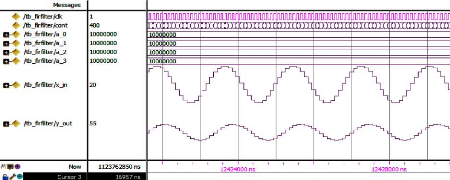

2ème simulation

Avec les paramètres suivants nous avons les

résultats de simulation de la figure III.11 :

· Horloge : 100ns

· Largeur des données : 8 bits

· Pas de comptage : 60

Soit un cosinus d'une fréquence de 500kHz

Figure III.12 : Résultats de la

simulation d'un filtre du 3ème ordre avec f=500khz

|