III.4 Synthèse et implémentation

Le but de notre projet étant d'implanter un filtre

numérique dans un FPGA, nous allons essayer de faire cette étape

du travail dans cette section en implantant de dernier filtre RIF qu'on a

développé en VHDL ; nous avons choisit comme support

d'élaboration les FPGA de type Xilinx Virtex XCV50. Pour cela, il faut

travailler avec le logiciel de développement Xilinx ISE 8.1.

Pour accomplir notre projet sous Xilinx ISE il faut suivre les

étapes suivantes :

> Créer le projet : nous

avons pris les mêmes fichiers VHDL que celui développé en

III.3, et nous l'avons adapté à pour qu'il soit compilable sous

Xilinx.

> Compilation (compile) : c'est

l'étape de vérification de la syntaxe et structure des codes

VHDL.

> Synthèse et optimisation :

Il s'agit de réaliser le circuit RTL (Registre-Transfert level) avec des

primitives technologiques (CLB, blocs RAM, I/O).

> Placement-routage : Le

rôle du placement-routage est double. Cibler les différentes

primitives existantes dans le FPGA choisit. Et faire les différentes

connexions entre les ces primitives.

Pour effectuer toute ces opérations, il faut en

premier valider le FPGA avec le quel nous allons travailler, qui est le Virtex

XCV50, Le tableau suivant présente les différentes

caractéristiques de cette FPGA.

Le filtre étant générique, il faut lui

fixé ses paramètres avec les valeurs suivantes

· Nombre de coefficient = 8

· Largeur du bus de données = 4 bits

Tableau III.2 : Les caractéristiques de circuit

programmable FPGA (virtex : xcv50)

|

composant

|

portes

logiques

|

CLB

|

Cellules

logiques

|

E/S

disponible

|

RAM

|

Performance

système

|

|

Xcv50

|

57,906

|

16x24

|

1.728

|

180

|

32.768

|

200 Mhz

|

L'étape de la synthèse nous donne le schéma

logique du filtre RIF qu'on a développé.

Figure III.16 - Schéma RTL

équivalent du FIR à xcv50 sous Xilinx ISE 8.1i L'exécution

des différentes étapes de synthèse et placement-routage se

résume dans le

tableau suivant :

Tableau III.2 : Les caractéristiques de

circuit programmable FPGA (virtex : xcv50) qui est utilisée :

|

Utilisation élément logique

|

utilisé

|

Existant

|

pourcentage

|

|

Numbers ne bascules

|

24

|

1,536

|

1%

|

|

LUTs (table de vérité)

|

285

|

1,536

|

18%

|

|

Distribution logique

|

|

|

|

|

Nombre de CLB utilisé

|

185

|

768

|

24%

|

|

Nombres total de LUTs à 4

entrées

|

318

|

1,536

|

20%

|

|

Nombres des entrées sorties

|

48

|

94

|

51%

|

|

Nombres d'horloges

|

1

|

4

|

25%

|

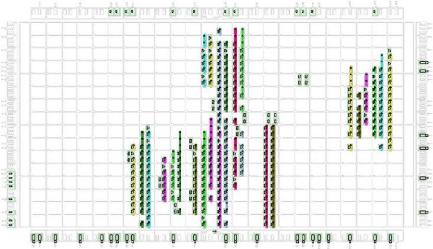

Le résultat du placement-routage est donné sur la

figure suivante :

Figure III.17 - Implantation de filtre RiF sur

un circuit FPGA (xcv50)

|