I.4. Les principes du langage VHDL

E1

Entré

E2

Structure

Logique

Sortie

Un opérateur élémentaire, un circuit

intégré, une carte électronique ou un système

complet sont intégralement définis par des signaux

d'entrées et de sortie et par la fonction design entity qu'ils

réalisent de façon interne. L'élément essentiel de

toute description en VHDL, nommée dans le langage, est formé par

le couple ENTITY ;ARCHITECTURE. Le premier élément de ce couple

décrit l'apparence externe d'une unité de conception, le second

décrit son fonctionnement interne. [3]

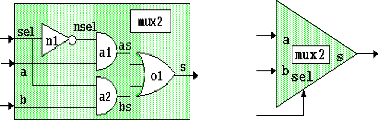

Figure I.1 : Boite noire Fgure I1 : Bo

Exemple

Un multiplexeur 2 voies vers 1

Figure I.2 un multiplexeur 2 voies vers 1

I.4.1. Déclaration des bibliothèques

Toute description VHDL utilisée pour la synthèse

a besoin de bibliothèques. Et plus particulièrement la

bibliothèque IEEE 1164. Elle contient les définitions du type de

signaux électroniques, fonctions et sous programmes permettant de

réaliser des opérations arithmétiques et logiques. Les

bibliothèques sont spécifiées par le mot clé

library. Pour avoir

Accès a une partie de la bibliothèque on utilise

l'énoncé use. On a donc accès dans l'entité

Incrémenter à tous les types définis dans le package

std_logic_1164 de la libraire IEEE. Cela nous permet entre autres d'utiliser le

type std_logic. [4]

|

Library ieee ;

Use ieee.std_logic_1164.all; Use ieee.numeric_std.all

;

Use ieee.std_logic_unsigned .all;

|

I.4.2. L'entrée de la boîte noire :

Entité

La déclaration d'entité décrit

l'interface entre le monde extérieur et une unité de conception.

C'est a dire principalement ses signaux d'entrée et de sortie. Une

même entité peut être associée à plusieurs

architectures différentes. Elle décrit alors une classe

d'unités de conception qui présente au monde extérieur le

même aspect, avec des fonctionnements internes éventuellement

différents. [5]

La déclaration d'entité :

La syntaxe générale d'une entité

|

ENTITY Nom de l'ejité

IS

GENERIC (le nom du signal : type :=la valeur);

Port (nom du signal : direction type) ;

END Non de l'ejité ;

|

+ On spécifie ici le nom de l'entité

créée. Ce nom est choisi par le programmeur. Les mots

entity et is sont des mots

clés du langage VHDL. Ils indiquent le début de la description

d'un nouveau design en VHDL.

+ L'instruction GENERIC permet de

spécifier certains paramètres de l'entité, comme par

exemple la largeur d'un bus. Le paramètre peut être

initialisé directement dans l'entité à une certaine

valeur, puis modifié ultérieurement lors le son utilisation. De

cette manière la description peut rester très

générale.

+ l'instruction port permet de

décrire les entrées sorties.

? Nom du signal : Il est composée de

caractères, le premier caractère doit être une lettre, sa

langueur est quelconque, mais ne doit pas dépasser une ligne de code.

· La direction du signal

> In : pour un signal

d'entrée.

> Out : pour un signal de sortie. Une sortie

ne peut être reliée à l'intérieur de l'architecture

associée à l'entité

> Inout : pour un signal en entrée

sortie, la connexion peut alors être reliée et

réutilisée à l'intérieur de l'architecture

associée.

· Le type

La notion de type est très importante en VHDL, chaque

entrée, sortie, signal, variable ou constante, est associé

à un type. Sans artifice particulier, il n'est pas question d'effectuer

une opération entre deux grandeurs de type différent.

> Bit : Il s'agit là,

évidemment, du type de base le plus utilisé en

électronique numérique. Un objet de type bit peut prendre deux

valeurs : '0' et '1', il s'agit, en fait, d'un type

énuméré prédéfini.

> Bit_vector : un vecteur de bits est un bus

déclaré par exemple pour une largeur de N bits par bit_vector (N

downto 0) ou bien bit_ vector (0 to N)

La fin de la déclaration de l'entité est

indiquée avec le mot réservé end. Il est

facultatif de placer ensuite le nom de l'entité, mais c'est une bonne

habitude de le faire pour que les programmes soient plus clairs et faciles

à lire.

Exemple du multiplexeur de la figure I.2 :

La déclaration de l'entité du multiplexeur 2 voies

vers 1 ENTITY multiplexeur IS

PORT (a, b: in bit ;

S: out bit);

End multiplexeur;

Où:

|