I.5.2. Les instructions séquentielles

Comme tout langage de programmation, VHDL possède des

instructions séquentielles de contrôle. Elles sont au coeur des

descriptions comportementales des circuits plus que jamais, dans ce type de

description, il est essentiel de toujours avoir présente a l'esprit

l'architecture du circuit que l'on décrit : ses signaux d'horloge, ses

registres, ses blocs combinatoire.

Les principales instructions séquentielles sont :

L'affectation séquentielle d'un signal, qui utilise

l'opérateur « <= ~, a une syntaxe qui est identique a celle de

l'affectation concurrente simple. Seule la place, dans ou hors d'un module de

programme séquentiel, distingue les deux types d'affectation ; cette

différence, qui peut sembler mineure, cache des comportements

différents : alors que les affectations concurrentes peuvent être

écrites dans un ordre quelconque, pour leurs correspondantes

séquentielles, rarement utilisées hors d'une structure de

contrôle, l'ordre d'écriture n'est pas indifférent.

· L'affectation d'une variable, qui utilise

l'opérateur « := > est toujours une instruction

séquentielle.

· Les tests << if > et

<< case >.

· Les instructions de contrôle des boucles

<< loop >, <<

for >.

1) Les instructions de test

Les instructions de test permettent de sélectionner

une ou des instructions à exécuter, en fonction des valeurs

prises par une ou des expressions. On notera que, dans un processus, si toutes

les branches possibles des tests ne sont pas explicitées, une cellule

mémoire est générée pour chaque affectation de

signal.

2) L'instruction « if....then....else....end if

» :

L'instruction if permet de sélectionner une ou des

instructions a exécuter, en fonction des valeurs prises par une ou des

conditions.

Syntaxe :

If expression_1

then

Instructions séquentielles [Elsif

expression_2 then]

Instructions_séquentielles [else]

Instructions_séquentielles; End if

;

3) L'instruction « case....when....end case

>>

L'instruction case permet de sélectionner une ou des

instructions a exécuter, en fonction des valeurs prises par une

expression.

Syntaxe :

Case expression is

when valeur1 =>

instruction sequentielle ;

when

valeur2 => instruction sequentielle

;

....

when others => instruction

sequentielle

End case ;

|

|

Il faut toujours mettre un « when others

». Cela permet de couvrir tous les cas de figure, et donc de ne

pas avoir des états indéterminés.

Exemple du multiplexeur (fig I.2)

Case sel is When `0' =>

S<= a;

When `1' =>

S<= b;

End case;

4) Boucle « for »

Les boucles permettent de répéter une

séquence d'instructions. Syntaxe : FOR

parametre IN intervalle

LOOP

Instructions séquentielles ;

END LOOP ;

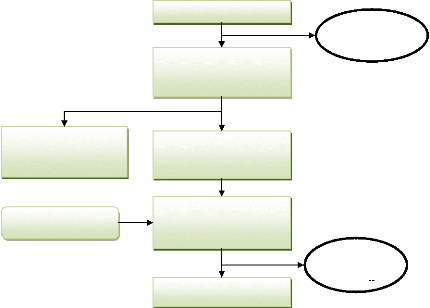

Les différentes étapes de la conception d'un

circuit intégré sont illustrées par le diagramme de la

figure I.3

L'ensemble du processus qui permet de passer de la vision

fonctionnelle au circuit constitue la synthèse.

Le premier outil utilisé dans les étapes de

synthèse automatique est un éditeur de texte avec lequel on

décrit le comportement du circuit logique en langage VHDL. Ensuite, la

description VHDL est traduite par l'outil de synthèse. Cette

étape est très importante, il s'agit de convertir la description

de haut niveau (VHDL) en fonction logique. Le synthétiseur

génère en sortie une liste d'interconnexion de composants

logiques de base existant dans la technologie cible choisie. Finalement

l'intégration physique dr descrription est effectuée dans le

circuit programmable.

Nous spécifions trois étapes de simulation soit :

> Simulation VHDL.

> Simulation fonctionnelle.

> Simulation temporelle.

La simulation VHDL est rapidement réalisée car

elle ne nécessite par de synthèse de la description. Elle sera

toujours exécutée. Cette simulation est très utile si le

fonctionnement de la description VHDL n'est pas modifié par

l'étape de synthèse. L'objectif principal de cette simulation est

de donner au lecteur la maitrise de cette description en vue de la

synthèse automatique.

La simulation a été effectuée avec le

logiciel ModelSim de la société Model

Technology. L'utilisation d'un autre simulateur ne pose pas de problème

particulier si celui-ci supporte la norme VHDL-93 et dispose des paquetages

Std_Logic_1164 et Numeric_Std.

Finalement, il sera nécessaire d'exécuter une

simulation après synthèse. La simulation fonctionnelle ne sera

pas réalisée. Nous ferons uniquement la simulation temporelle qui

utilise le résultat après placement et routage .Cela nous

permettra de valider que toute la chaine s'est correctement

déroulée. [6]

Technologie cible

Simulation VHDL

(MODELSIM )

Vision fonctionnelle

Description

(Modèle structurel)

Traduction (Modèle VHDL)

Circuit cible

Compilateur

Simulation

Simulation fonctionnelle

Figure : I.3- Flot de conception basé sur

VHDL

|