4.5.3 Technique de contrôle utilisant le

système de boucle à verrouillage de phase (PLL)

La mise au point de la technique de boucle à

verrouillage de phase en Anglais PLL (Phase Locked Loop) est directement

liée à l'histoire de la modulation d'amplitude. Le principe de la

PLL a été étudié en 1932, par Henri De BELLISCISE

un ingénieur de l'École Supérieure

d'Électricité (invention française). Ce dispositif

était destiné à améliorer les conditions de

réception des signaux radioélectriques noyés dans le bruit

en modulation d'amplitude. A l'époque, les réalisations à

base de PLL étaient à tubes et donc volumineuses, chères

et réservées au matériel professionnel. Aujourd'hui, la

technique PLL ne comprend plus qu'un circuit

intégré et quelques composants

périphériques. Les PLL ont envahi tout le domaine

des télécommunications.

1. Aperçu général

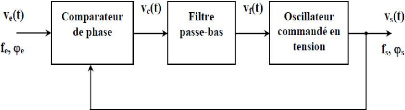

Le système PLL contient 3 composants de base (Fig.4.13)

:

- un comparateur de phase (CDP);

- un filtre passe-bas (FPB);

- un oscillateur contrôlé en tension (VCO).

62

Figure 4. 14 : Structure de base de la boucle à

verrouillage de phase

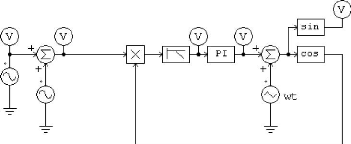

2. Système de contrôle PLL sur Psim

Figure 4. 15 : Conception PLL dans la plateforme du

logicielle Psim

4.5.4 Synchronisation de l'onduleur connecté au

réseau à l'aide de la

technique PLL

La méthode de boucle à verrouillage de phase

(PLL) est considérée comme un appareil qui permet à un

signal de suivre un autre. Le signal de sortie se synchronise avec un signal

d'entrée de référence en fréquence et en phase. La

boucle de contrôle de courant est basée sur le contrôleur PI

(intégrale proportionnelle) et la PLL est chargée de lui fournir

les signaux. Pour que la PLL synchronise la fréquence du signal

d'entrée périodique et l'angle de phase avec le signal de sortie,

elle utilise un oscillateur

63

interne identifié comme oscillateur commandé en

tension et une rétroaction négative. L'angle de phase, la

fréquence et la tension du réseau sont identifiés par le

système PLL. Afin de mettre en oeuvre les transformations de trame de

référence synchrone, l'angle de phase est nécessaire

tandis que la fréquence et la tension sont nécessaires pour la

stabilité dynamique du système et de surveiller les conditions du

réseau. Cependant, les courants sont transformés en

référentiel synchrone dq, qui effectue un processus de

découplage entre les axes d et q.

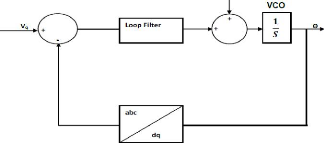

Une configuration courante pour la synchronisation du

réseau utilisée de nos jours est la boucle à verrouillage

de phase (PLL) implémentée dans le référentiel

synchrone dq et son schéma est illustré dans la figure 4.16

ci-dessous. Cette configuration de PLL est composée de la

détection de phase et du filtre de boucle. La mise en oeuvre de la

détection de phase peut être réalisée en utilisant

la transformation abc en dq dans le système triphasé.

Alternativement, la dynamique du système est déterminée

par le filtre de boucle. Cependant, la bande passante du filtre est un accord

entre les performances du filtre et la réponse temporelle. Par

conséquent, la qualité du verrou et la dynamique PLL sont

fortement influencées par les paramètres du filtre de boucle

(Meersman et al. 2010; Timbus et al. 2005).

Figure 4. 16 : Représentation PLL dans un

référentiel synchrone

De plus, le référentiel synchrone peut

facilement obtenir une performance appropriée et de petites erreurs

d'état stationnaire en amplitude et en phase avec une configuration de

compensateur simple car en état stationnaire les signaux sont sous forme

de courant continu (Reznik 2012; Chung 2000).

Habituellement, le réseau électrique public est

un système rigide dans lequel toute déviation de la

fréquence fournie entraîne une augmentation de l'erreur de l'angle

de phase. Cette erreur est réduite à zéro en utilisant le

contrôleur PI (Kaura & Blasko

64

1997). La réponse en boucle fermée de

l'algorithme PLL peut prédire entièrement la réponse aux

fluctuations de fréquence.

|