|

Table des matières

Table des matières

I. Introduction

général..................................................................

4

II. Motivation du choix du

thème................................................................

5

III. Objectif

.............................................................................................

5

Chapitre I : généralités sur les

systèmes embarqués

1.

Définitions.............................................................................................

7

2. Historique 8

3. Classe des systèmes

embarqués..................................................................

10

4. Caractéristiques des systèmes

embarqués.................................................................10

5. Contraintes des systèmes

embarqués................................................................

11

6. Architecture des systèmes

embarqués............................................................

12

1. Les systèmes embarqués de première

génération........................... 12

2. Les systèmes embarqués de deuxième

génération.............................................13

3. Les systèmes embarqués de troisième

génération.............................................14

7. Les systèmes embarqués

spécifiques.........................................................

15

Chapitre II : conception des logiciels

embarqués

1.

Introduction..........................................................................................

17

2. Les systèmes pour puces 17

3. La conception des systèmes sur puces 20

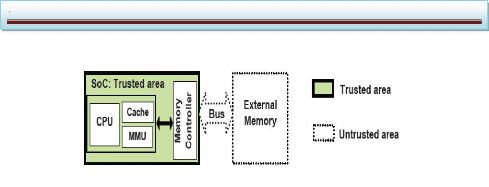

4. Les systèmes monopuces (SoC)... 22

5. Conception des systèmes

embarqués......................................................

23

1. Flots classiques de conception des

SE.......................................... 23

2. Flots de conception récents 25

6. Exemple de flot de conception pour

SoC................................................ 26

1. Présentation générale 27

2. Architecture détaillée du flot

...................................................... 31

7. De la compilation au ciblage du logiciel 35

1. Introduction sur la

compilation.....................................................................35

2. Le ciblage logiciel en

général......................................................

37

3. Représentations pour le ciblage logiciel

38

4. Le ciblage logiciel pour les architectures

spécifiques 41

8. Etat de l'art sur les systèmes d'exploitation

OS............................................. 48

1. Introduction sur les systèmes d'exploitation

48

2. Systèmes d'exploitation définitions

48

9. Les systèmes d'exploitation dans les

systèmes embarqués.......................................

50

1. Fonctionnalités requises pour le logiciel dans les

SE........................... 51

2. Contraintes imposées par les SE pour le logiciel

54

3. Les degrés de liberté pour le logiciel dans

les SE 56

4. Exemples de SE généralistes 56

5. Avantages et inconvénients des OS pour les SE

57

10. Conclusion 59

Chapitre III : conception matériel

1. Introduction 61

2. Modéliser et synthétiser à un haut

niveau 61

3. Réutilisation de composants matériels

63

1. Composants

virtuels.................................................................................

63

2. Standardisation 64

4. Un exemple d'environnement orienté composante pour

la conception

d'architecture

numérique..............................................................................

65

5. L'état de lieux de perspectives de

recherche......................................................... 67

6. Architecture

matérielle...........................................................................

68

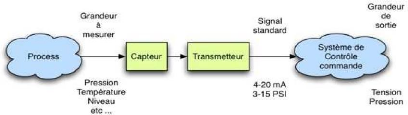

1. Les capteurs 69

2. Les convertisseurs analogiques numériques

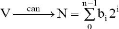

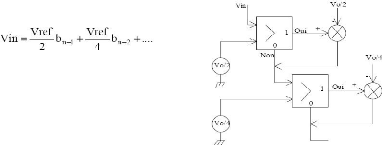

70

3. Effecteurs : influent sur l'environnement 72

4. Interface homme machine 73

5. Interfaces

associées..................................................................

73

6. Les

mémoires....................................................................................

73

7. Circuit logique programmable « FPGA

»............................................. 74

8. Unité centrale de traitement « CPU »

74

7. Conclusion 75

Chapitre IV : sécurité des systèmes

embarqués

1.

Introduction.............................................................................................

77

2.

Cryptologie......................................................................................................

77

1.

Introduction..............................................................................

77

2.

Confidentialité.................................................................................

78

3. Intégrité et authentification 78

3. Les menaces de sécurité

....................................................................................

79

1. Types d'attaques

(menaces)..................................................................

79

2. Objectifs des

attaques...............................................................

79

3. Classement des

attaques............................................. 79

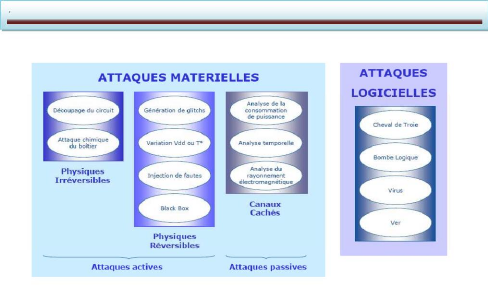

4. Contre mesure 82

5.

Conclusion................................................................................................

83

Conclusiongénéral..................................................................

84

Bibliographie

........................................................................

85

Glossaire...................................................................................................

86

Table des figures

Table Des Figures

Chapitre I

Figure a : Système de régulation de

quantité de

vapeur............................................................ 8

Figure b : Le premier système embarqué

9

Figure c : Le système de contrôle aux LGM-30

Minuteman............................................................ 9

Figure I.1 : Un système embarqué dans son

environnement................................................... 11

Figure I.2 : Architecture embarquée de première

génération

..........................................................12

Figure I.3 : Architecture embarquée de deuxième

génération.............................................

13

Figure I.4 : Architecture embarquée de

troisième génération....................................

14

Chapitre II

Figure II.1 : Architecture logicielle/matérielle d'un

SoC................................................ 19

Figure II.2 : Les métiers de la conception

système

......................................................................20 Figure

II.3 : Le flot de conception

système................................................................................21

Figure II.4a : Les flots de conception classiques pour les

SE..........................................................24 Figure II.4b :

codéveloppement pour les

SE..............................................................................24

Figure II.5 : Les deux méthodes de cosimulation

...................................................... 26 Figure II.6 : La

représentation

intermédiaire.............................................................................28

Figure II.7 : Exemple de description pour chaque niveau

d'abstraction ......... 29

Figure II.8 : représentation simplifiée du flot

de conception pour SoC................................. 30

Figure II.9 : Un module

processeur........................................................................................31

Figure II.10 : Le flot de conception générale

pour les SoC................................................ 32

Figure II.11 : Génération d'interfaces

matérielles et logicielles.......................................

34

Figure II.12 : Enveloppes de

simulation..................................................................

35

Figure II.13 : Les étapes de la compilation d'un

programme en langage C........................................37 Figure II.14 :

Les étapes du ciblage

logiciel..............................................................................40

Figure II.15 : OS en tant qu'abstraction du

matériel................................................... 49

Figure II.16 : OS en tant que gestionnaire de ressources

................................................ 50

Figure II.17 : Communication point à point et

communication multipoint ........................ 52

Figure II.18 : Files d'attentes FIFO pour

désynchroniser deux blocs ................................. 53

Chapitre III

Figure III.1 : Système embarqué typique

..................................................................................68

Figure III.2 : Capteur et transmetteur en situation

......................................................................69 Figure

III.3 : Principe de la pesée successive

............................................................................70

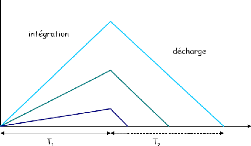

Figure III.4: Principe du convertisseur simple rampe

...................................................................71 Figure

III.5: Architecture du convertisseur double rampe

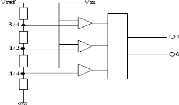

......................................................... 71 Figure III.6 : Le

convertisseur flash

........................................................................................72

Chapitre IV

Figure IV.1 : Classement des attaques

....................................................................................80

Figure

IV.2 : Modèle de menaces

..........................................................................................81

Figure

IV.3 : Types de

menaces..............................................................................................81

Listes des tableaux

Tableau II.1 : Exemple de description pour chaque niveau

d'abstraction...........................................28

Introduction général

I. Introduction général :

Un système embarqué est un système

électronique et informatique autonome ne possédant pas des

entrées/sorties standards comme un clavier ou un écran

d'ordinateur. Il est piloté dans la majorité des cas par un

logiciel, qui est complètement intégré au système

qu'il contrôle. On peut aussi définir un système

embarqué comme un système électronique soumis à

diverses contraintes. Les concepteurs des systèmes électroniques

sont aujourd'hui confrontés à la complexité croissante des

algorithmes mis en oeuvre et à la variété des cibles

potentielles FPGAs et/ou DSPs. Actuellement, il n'est pas rare que ces

systèmes intègrent plusieurs douzaines voire des centaines de

processeurs. A l'origine, ce sont des systèmes matériels et

logiciels intégrés dans des avions militaires ou des missiles.

Ensuite dans le civil: avions, voitures, machine à laver...! La machine

et le logiciel sont intimement liés et noyés dans le

matériel et ne sont pas aussi facilement discernables comme dans un

environnement de travail classique de type PC. On mentionne les contraintes

physiques fortes: dimensions, poids, taille, autonomie, consommation,

fiabilité, contraintes temporelles (temps réels).

Le premier chapitre est une introduction

générale à ce domaine pluridisciplinaire. Après en

avoir posé les grands principes avec des

généralités, en effet, l'électronique se trouve

maintenant embarquée dans de très nombreux objets usuels : les

téléphones, les agendas électroniques, les voitures. Ce

sont ces systèmes électroniques enfouis dans les objets

usuels.

Le deuxième chapitre est consacré à la

conception des logiciels embarqués, les habitudes de programmation pour

les ordinateurs portent à croire que la compilation et l'édition

de liens sont les seuls traitements à apporter au logiciel pour pouvoir

le faire fonctionner sur une architecture cible. Le but de ce chapitre est de

montrer que dans le cas des systèmes embarqués, une autre

étape est nécessaire avant la compilation : elle adapte le

logiciel à l'architecture cible spécifique et sera nommée

dans ce mémoire le ciblage logiciel.

Dans le troisième chapitre, nous nous

intéresserons aux bases de conception matérielle. En effet, les

systèmes à base de composants apparaissent bien dans une

architecture matérielle qui est vue comme l'interconnexion sur une carte

(PCB pour Printed Circuit Board) de composants sur étagère vendus

dans des boîtiers séparés. Ces composants sont vus comme

des boîtes noires auxquelles les constructeurs associent des documents

(datasheets, notes d'application), pour en préciser les

fonctionnalités, les interfaces et les contraintes d'utilisation. Une

même carte regroupe généralement un processeur, de la

mémoire, des périphériques de taille modeste et des

circuits logiques. Ces derniers sont combinés soit pour construire des

circuits plus complexes, soit sous forme de «glu» pour adapter les

interfaces entre composants.

Le quatrième chapitre traite des problèmes sur

la sécurité des systèmes embarqués. On cite

notamment : La cryptologie qui est la science du secret, elle se divise en deux

branches : La cryptographie : qui étudie les différentes

possibilités de cacher, protéger ou contrôler

l'authenticité d'une information; La cryptanalyse : qui étudie

les moyens de retrouver cette information à partir du texte

chiffré (de l'information cachée) sans connaître les

clés ayant servi à protéger celle-ci, c'est en quelque

sorte l'analyse des méthodes cryptographiques.

Le besoin des entreprises internationales installées en

Algérie, dans les nouvelles technologies de l'information et de la

communication, et spécialement dans le domaine de conception des

systèmes embarqués, c'est dans ce contexte qu'on a

étudié ce thème qui a pour but le transfert de

compétence dans le domaine des systèmes embarqués.

Internationalement, Les multiprocesseurs sur monopuce paraient être une

voie prometteuse, ils introduisent de nouvelles contraintes et de nouveau

défis à soulever, due essentiellement à leurs natures

multi-coeurs.

Motivation et Objectif

Motivation :

Les systèmes embarqués prennent une place de

plus en plus importante dans notre société, ils servent à

contrôler, réguler des dispositifs électroniques

grâce à des capteurs, embarqués dans des robots, des

véhicules spatiaux, etc. Ces systèmes embarqués sont

souvent utilisés par le public dans la vie de tous les jours sans

même qu'on ne s'en rende compte, par exemple dans les systèmes de

freinage d'une voiture, le contrôle de vol d'un avion,... Et grâce

a cette importance des systèmes embarqués on a choisis ce

thème la.

IV. Objectif :

Notre but principal est la conception des systèmes

embarqués en général par l'étude des points

suivants :

- Bien connaitre les systèmes embarqués.

- Les flots de conception existant des systèmes

embarqués.

- Les systèmes d'exploitation dédiés aux

systèmes embarqués. - L'architecture matérielle des

systèmes embarqués.

- La sécurité des systèmes

embarqués.

Chapitre I

Généralités sur les

systèmes

embarqués

Chapitre I

généralités sur les systèmes

embarqués

I.1. DEFINITIONS :

Définition 1 :

Les systèmes électroniques sont de plus en plus

présents dans la vie courante. Les ordinateurs et micro-ordinateurs sont

des systèmes électroniques bien connus. Mais

l'électronique se trouve maintenant embarquée dans de très

nombreux objets usuels : les téléphones, les agendas

électroniques, les voitures. Ce sont ces systèmes

électroniques enfouis dans les objets usuels qui sont appelés

systèmes embarqués.

Définition 2 :

« Embedded system » tout système conçu

pour résoudre un problème ou une tache spécifique mais

n'est pas un ordinateur d'usage général.

-Utilisent généralement un microprocesseur

combiné avec d'autres matériels et logiciel pour résoudre

un problème de calcul spécifique.

-Système électronique et informatique autonome ne

possédant pas des entrées-sorties standards.

-le système matériel et l'application sont

intimement liés et noyés dans le matériel et ne sont

discernables comme dans un environnement de travail classique de type PC.

Définition 3 :

N'est pas visible en tant que tel, mais est

intégré dans un équipement doté d'une autre

fonction ; ou dit aussi que le système est enfoui, ce qui traduit plus

fidèlement le terme anglais « Embedded ».

-Une faible barrière existe entre les systèmes

embarqués et les systèmes temps réel (un logiciel

embarqué n'a pas forcément de contraintes temps réel).

-La conception des ces systèmes est fiable (avions,

système de freinage ABS) à cause de leur utilisations dans des

domaines à fortes contraintes mais également parce que

l'accès au logiciel est souvent difficile une fois le système

fabriqué.

Définition 4 :

Les microprocesseurs s'étendent depuis de simples

microcontrôleurs 8bits aux 64bit le plus rapidement et les plus

sophistiqués.

-le logiciel système inclus s'étend d'un petit

directeur à un grand logiciel d'exploitation en temps réel (RTOS)

avec une interface utilisateur graphique (GUI). Typiquement, le logiciel

système inclus doit répondre aux événements d'une

manière déterministe et devrait toujours être

opérationnel.

Les systèmes embarqués couvrent aussi bien les

commandes de navigation et de commande de trafic aérien qu'un simple

agenda électronique de poche.

I.2. HISTORIQUE :

La plupart des machines qui nous simplifient la vie ont besoin

d'un système de régulation ou de contrôle pour fonctionner

de manière correcte.

Ces systèmes de contrôle existent depuis bien avant

l'invention des ordinateurs. Exemple :

Pour maintenir une locomotive à vapeur à une

vitesse constante, on a besoin d'un système qui régule la

quantité de vapeur envoyée dans les pistons.

Si la locomotive ralentit (pente montante...) il faut injecter

plus de vapeur, si la locomotive accélère, il faut injecter moins

de vapeur On aimerait que cette tâche se fasse de façon

«automatique», c'est-à dire avec un minimum d'intervention de

l'être humain.

Solution : le gouverneur à force centrifuge

valve valve

d'admission d'adminission

de vapeur de vapeur

axe relié aux roues rotation rapide

fermeture

Figure a : Système de régulation de

quantité de vapeur

Ces systèmes de contrôle peuvent donc être

réalisés de manière forte simple. Avec le

développement de la technologie, on a opté pour des

systèmes basés sur l'électronique.

Parallèlement à ce développement des

systèmes de contrôle, les systèmes informatiques se sont

développés. Ceux-ci sont vite sortis du cadre des «machines

de bureau» ou de «machine à calculer» dans lequel ils

avaient initialement été développés, (Ordinateur =

machine à traiter l'information).

Il est donc naturel d'utiliser les possibilités de

calcul de l'ordinateur comme composant d'un système plus large. Pour

remplacer un système de régulation analogique, et pour

réaliser un traitement qui serait trop complexe / impossible en

analogique...

Les Avantages:

· plus grande flexibilité des systèmes

informatiques.

· On peut modifier le programme.

· On peut réutiliser plus facilement ce qui existe

déjà.

· plus de puissance de calcul.

· plus compact.

Sys. Contrôle Informatique

Systèmes embarqués

Un des premiers exemples de système embarqué

date du début des années 1960. Il s'agit de l'ordinateur de bord

des vaisseaux spatiaux du programme Apollo, qui a amené N. Armstrong sur

la lune. Cet ordinateur contrôlait en temps réel les

paramètres de vol et adaptait la trajectoire. Il fonctionnait en mode

interactif.

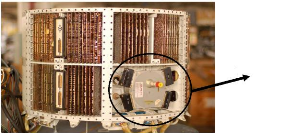

|

Interface utilisateur

Pas de CPU: plus de 4000 circuits intégrés

contenant chacun 3 portes NOR 32 Ko de RAM

72 Ko de ROM 2MHz

Programme en assembleur (11 instructions)

|

Figure b : Le premier système

embarqué

Le premier système embarqué qui a

été produit en série est vraisemblablement le D-17

d'Autonetics. Il servait de système de contrôle aux missiles

nucléaires américains LGM-30 Minuteman, produit à partir

de 1962.

Disque dur

Figure c : Le système de contrôle aux

LGM-30 Minuteman Le disque était utilisé comme

mémoire primaire !

Depuis les systèmes se sont diversifiés, ils ont

permis l'explosion du marché des «consumer

electronics» où tout est (devenu) numérique (GSM,

électroménager, MP3s, etc.). Ils sont également bien

présents dans le domaine industriel pour Contrôle de processus de

production, etc.

La convergence entre les applications électroniques

pour grand public et les ordinateurs est de plus en plus grande : La console de

jeu XBox de Microsoft n'est qu'un PC «emballé» sous la forme

d'une console. Il est de plus en facile de transformer son PC de bureau en

«media center» qui remplace la chaîne hi-fi et le

lecteur DVD...

Brève histoire des systèmes

embarqués :

1967 : Apollo Guidance Computer, premier système

embarqué. Environ un millier de circuits intégrés

identiques (portes NAND).

1960-1970 : Missile Minuteman, guidé par des circuits

intégrés.

1971 : Intel produit le 4004, premier microprocesseur, à

la demande de Busicom. Premier circuit générique, personnalisable

par logiciel.

Chapitre I généralités sur les

systèmes embarqués

1972 : lancement de l'Intel 8008, premier microprocesseur 8 bits

(48 instructions, 800kHz).

1974 : lancement du 8080, premier microprocesseur largement

diffusé. 8 bits, (64KB d'espace adressable, 2MHz - 3MHz).

1978 : création du Z80, processeur 8 bits.

1979 : création du MC68000, processeur 16/32 bits.

I.3.Classes des systèmes embarqués

: > Calcul normal (limite de

matériels) - Application similaire à une

application de bureau mais empaquetée dans un système

embarqué.

- Les jeux de vidéo, set- top box, et TV Box. >

Les systèmes de contrôle

- Contrôle de systèmes en Temps Réel.

- Moteur d'automobile, traitement chimique, traitement

nucléaire, système de navigation aérien.

> Traitement de signal

- Calcul sur de grosses quantités de données.

- Le radar et sonar, le dispositif de compression

vidéo.

> Télécommunications &

Réseau

- Transmission d'information et commutation. -

Téléphone portable, Dispositifs de l'Internet.

I.4.Caractéristiques des systèmes

embarqués :

La principale caractéristique d'un système

embarqué est qu'il est conçu pour gérer quelques

tâches simples, mais les étapes de la manipulation ou de

l'accomplissement de cette tâche mai être aussi complexe que tout

programme d'ordinateur. Un contrôleur de jeux vidéo, par exemple,

mai être considérés comme ayant des tâches simples,

charge le jeu et permettre au joueur de contrôler par le biais de

commandes entrées par l'intermédiaire du combiné. En

vérité, cependant, un contrôleur de jeu (surtout les

nouveaux jeux conçus pour la X-Box ou PS3) passe par une série de

mesures et d'actions qui nécessitent le plus de puissance de traitement

comme un ordinateur. Parmi les caractéristiques de modernes

systèmes embarqués sont:

Interface utilisateur

L'origine, un système intégré n'a pas

d'interface utilisateur, l'information et des programmes ont déjà

été intégrés dans le système (par exemple,

le système de guidage d'un missile balistique intercontinental ou ICBM)

et il n'y avait pas de nécessité d'intervention humaine ou de

l'intervention, sauf pour installer le dispositif de test.

De nombreux systèmes embarqués modernes ont

toutefois à grande échelle des interfaces utilisateur bien que ce

ne sont que des entrées de données, mais ne sont pas

censés fournir des fonctionnalités supplémentaires pour le

système, par exemple, un clavier QWERTY pour PDA utilisé pour

saisir des noms, adresses, numéros de téléphone et des

notes et même le plein la taille des

documents. Le moment PDA ordinateur de bureau, atteindre le plein

de fonctionnalités, mais ils mai ne sera plus considéré

comme les systèmes embarqués.

Simple Système Limité, qui provient de la

fonctionnalitéL'origine, cette

référence à des systèmes de base tels que les

interrupteurs, les petits

caractères ou des chiffres et les voyants affiche

uniquement pour but de montrer la «santé» du système

embarqué, mais il a également atteint un certain niveau de

complexité. Une caisse enregistreuse ou d'un guichet automatique avec la

technologie d'écran tactile est considéré comme un

système intégré, car il a des usages limités,

même si l'interface utilisateur (l'écran tactile) est un

système complexe.

CPU avec les plates-formes microprocesseurs ou de

microcontrôleurs

Encore une fois, la fonctionnalité limitée est

la clé dans la définition de ce que les systèmes

embarqués. Dans un sens, le BIOS est considéré comme un

système intégré, car il a des fonctions limitées,

et fonctionne automatiquement (quand l'ordinateur est démarré).

Périphériques comme l'USB peuvent aussi être

considérées comme des systèmes embarqués.

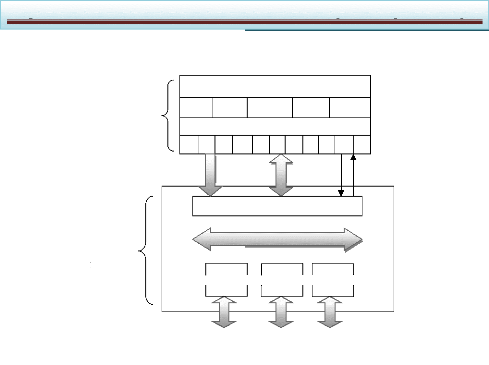

Les systèmes embarqués ont pour but de permettre

aux objets usuels de réagir à l'environnement. Ils peuvent aussi

apporter une interface avec l'utilisateur. La structure de base de ces

systèmes est donnée figure I.1 : l'environnement est

mesuré par divers capteurs. L'information des capteurs est

échantillonnée pour être traitée par le coeur du

système embarqué. Puis le résultat du traitement est

converti en signaux analogiques qui génèrent les actions sur

l'environnement (afficheur d'informations pour l'utilisateur, actionneurs,

transmission d'information, etc.).

Capteur

Capteur

Capteur

C

A

N

Environnement

Système

embarqué

Coeur

du

système

embarqué

C

N

A

Afficheur

Actionneurs

etc.

Figure I.1 : Un système embarqué dans

son environnement I.5. Les contraintes des systèmes

embarqués :

Les systèmes embarqués exécutent des

tâches prédéfinies et ont un cahier des charges

contraignant à remplir, qui peut être d'ordre :

De coût. Le prix de revient doit être le plus faible

possible surtout s'il est produit en grande

série.

Chapitre I généralités sur les

systèmes embarqués

D'espace compté, ayant un espace mémoire

limité de l'ordre de quelques Mo maximum. Il convient de concevoir des

systèmes embarqués qui répondent au besoin au plus juste

pour éviter un surcoût.

De puissance de calcul. Il convient d'avoir la puissance de

calcul juste nécessaire pour répondre aux besoins et aux

contraintes temporelles. Les processeurs utilisés dans les

systèmes embarqués sont 2 à 3 décades moins

puissantes qu'un processeur d'un ordinateur PC.

De consommation énergétique la plus faible

possible, due à l'utilisation de batteries et/ou, de panneaux solaires

voir de pile à combustible pour certain prototypes.

Temporel, dont les temps d'exécution et

l'échéance temporel d'une tâches est

déterminé (les délais sont connus ou bornés a

priori). Cette dernière contrainte fait que généralement

de tels systèmes ont des propriétés temps réel.

De sécurité et de sûreté de

fonctionnement. Car s'il arrive que certains de ces systèmes

embarqués subissent une défaillance, ils mettent des vies

humaines en danger ou mettent en périls des investissements importants.

Ils sont alors dits « critiques » et ne doivent jamais faillir. Par

« jamais faillir », il faut comprendre toujours donner des

résultats juste, pertinents et ce dans les délais attendus par

les utilisateurs (machines et/ou humains) desdits résultats.

I.6. Architecture des systèmes embarqués

:

Dans cette section, nous présentons les architectures

supportées par trois générations d'outils de

conception.

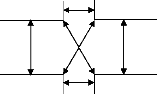

I.6.1. Les systèmes embarqués de

première génération :

I.6.1.1. Partie matérielle des systèmes

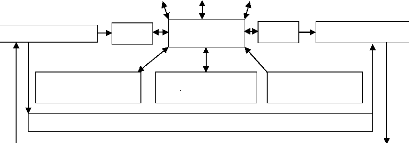

embarqués de première génération :

Les premiers systèmes embarqués supportés

par des outils tels que COSYMA et Vulcan étaient très simples :

ils étaient constitués d'un processeur qui contrôlait un

nombre restreint de CIAS (circuits intégrés à applications

spécifiques) ou ASIC qui étaient appelés

périphériques. Cette architecture est représentée

figure I.2. Les communications de cette architecture se situent au niveau du

bus du processeur et sont type maître/esclave : le processeur est le

maître et les périphériques sont les esclaves.

Système embarqué

Processeur

Périphérique

d'entrée

Mémoire

Bus du processeur

Périphérique

de sortie

Environnement

Figure I.2 : Architecture embarquée de

première génération

Les périphériques de ces architectures

étaient essentiellement des capteurs et des actionneurs

(contrôleurs magnétiques, sortie, etc.). Le processeur est

dédié au calcul et au contrôle de l'ensemble du

système.

Les microcontrôleurs assemblent sur une même puce le

processeur et les périphériques.

I.6.1.2. Partie logicielle des systèmes

embarqués de première génération :

Ne devant pas exécuter de nombreuses opérations

simultanées (le nombre de périphériques et de fonctions

étant restreint), les parties logicielles étaient

constituées d'un seul programme. La réaction aux

événements était effectuée par le biais de routines

de traitement d'interruptions.

Cette partie logicielle était décrite directement

en langage d'assemblage ce qui permettait d'obtenir un code efficace et de

petite taille.

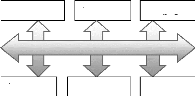

I.6.2. Les systèmes embarqués de

deuxième génération :

Les premiers systèmes embarqués ne pouvaient

fournir que des fonctions simples ne requérant que peu de puissance de

calcul. Leur architecture ne peut pas supporter les fonctionnalités

requises pour les systèmes embarqués actuels à qui il est

demandé non seulement d'effectuer du contrôle, mais aussi des

calculs complexes tels que ceux requis pour le traitement numérique du

signal. De nouveaux outils tels que N2C (dans ces nouvelles versions)

permettent de traiter des architectures plus complexes.

I.6.2.1. Partie matérielle des systèmes

embarqués de deuxième génération :

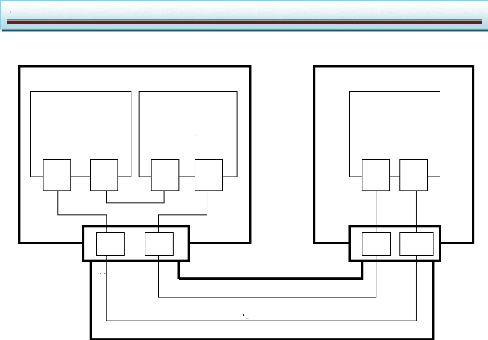

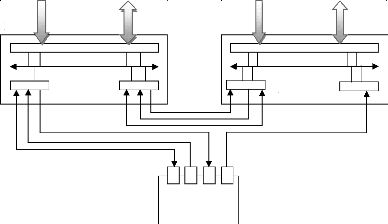

L'architecture des systèmes embarqués de

deuxième génération est composée d'un processeur

central, de nombreux périphériques, et souvent de quelques

processeurs annexes contrôlés par le processeur central. Le

processeur central est dédié au contrôle de l'ensemble du

système. Les processeurs annexes sont utilisés pour les calculs ;

il s'agit souvent de processeurs spécialisés comme les DSP. Une

telle architecture est représentée figure I.3. Dans une telle

architecture, plusieurs bus de communication peuvent être

nécessaires : chaque processeur dispose de son bus de communication.

Système embarqué

Processeur central

Périphériques d'entrée

Mémoire centrale

Bus annexe

Pont

Périphériques de sortie

Bus du processeur central

Mémoire annexe

Autres

périphériques

Processeur annexe

Environnement

Figure I.3 : Architecture embarquée de

deuxième génération

Chapitre I généralités sur les

systèmes embarqués

I.6.2.2. Partie logicielle des systèmes

embarqués de deuxième génération :

La partie logicielle des systèmes embarqués de

deuxième génération est répartie sur plusieurs

processeurs (le processeur principal et les processeurs annexes). Les

systèmes actuels sont trop complexes pour pouvoir être

gérés par un unique programme sur le processeur principal. Il est

donc nécessaire d'avoir une gestion multitâche sur ce processeur,

et un système d'exploitation est couramment employé dans ce

but.

Le logiciel du processeur central est souvent décrit

dans un langage de haut niveau tel que le C. le logiciel des processeurs

annexes est souvent trop spécifique pour être entièrement

décrit dans un langage de haut niveau, et l'utilisation des langages

d'assemblage est nécessaire.

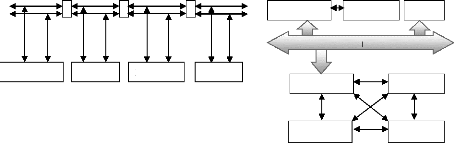

I.6.3. Les systèmes embarqués de

troisième génération :

Les progrès de l'intégration permettent

d'envisager des circuits pouvant contenir plusieurs milliers de portes. Il

devient donc techniquement possible de fabriquer des systèmes

embarqués pouvant remplir toutes les fonctionnalités

souhaitées.

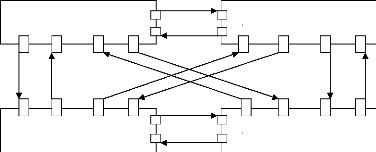

I.6.3.1. Parties matérielles des systèmes

embarqués de troisième génération :

Pour pouvoir supporter conjointement les besoins en puissance

et en flexibilité, ces architectures comprennent de plus en plus de

processeurs, qui peuvent chacun se comporter en maître : l'architecture

couramment utilisée, basée sur un processeur central

contrôlant le reste du système, n'est donc plus suffisante.

Processeur

ASIC

Processeur

Mémoire

Processeur

Mémoire

ASIC

Processeur

ASIC

Mémoire

Bus

Architecture à base de bus Architecture en barres

croisées

ASIC

ASIC

Mémoire

Processeur

Architecture à base de réseau

commuté

Mémoire

ASIC

Bus

Processeur

ASIC

Mémoire

ASIC

Processeur

Architecture mixte

Figure I.4 : Architectures embarquées de

troisième génération

Alors le goulet d'étranglement était les

ressources en calcul, de nos jours il est situé plutôt au niveau

des communications. Ce sont elles qui définissent désormais

l'architecture, et nos plus les ressources de calcul. La figure I.4 donne des

exemples d'architectures centrées sur les communications. Dans cette

figure, tous les éléments (processeur, ASIC ou mémoires)

sont traités de la même manière. Le premier exemple est

basé sur des communications par bus : ce modèle de communication

consomme peu de surface, mais risque de devenir un goulet

d'étranglement. Le deuxième est basé sur des

communications en barres croisées très performantes mais aussi

très coûteuses en surface. Le troisième exemple donne une

solution intermédiaire, par réseau commuté. Enfin le

dernier exemple montre qu'il est possible de mixer plusieurs modèles de

communication, et d'apporter de la hiérarchie dans l'architecture.

Autour de ce modèle d'architecture centré sur

les communications, se greffent les autres modèles d'architecture :

architectures des éléments de calcul et des mémoires.

L'architecture des éléments de calcul consiste à

définir quels sont les éléments principaux et quels sont

leurs périphériques de manière à les grouper dans

une architecture locale. L'architecture des mémoires sert à

définir quelles sont les mémoires locales à un groupe et

quelles sont celles qui seront partagées.

I.6.3.2. Parties logicielles des systèmes

embarqués de troisième génération :

Les parties logicielles ont beaucoup gagné en

importance dans les systèmes embarqués. Plusieurs systèmes

d'exploitation sont parfois nécessaires pour les divers processeurs de

l'architecture. De plus, la complexité et la diversité des

architectures possibles font qu'il devient de plus en plus nécessaire

d'abstraire les tâches logicielles des détails du matériel.

Toute cette complexité est donc reportée dans les systèmes

d'exploitation, qui deviennent de plus en plus complexes.

Cette complexité logicielle et matérielle

entraîne de nombreuses alternatives. En particulier, l'aspect

multiprocesseur apporte des alternatives pour les systèmes

d'exploitation : il peut y avoir un seul système pour tous les

processeurs (solution difficilement applicable lorsque les processeurs sont

hétérogènes), ou il peut y avoir un système par

processeur (solution qui peut être plus coûteuse).

I.7. Les systèmes embarqués

spécifiques :

Lorsqu'un système est utilisé pour une

tâche bien précise, il est souvent plus efficace et économe

s'il est spécifique à cette fonctionnalité que s'il est

général. Les systèmes embarqués sont très

souvent utilisés dans ces conditions, et il est donc intéressant

qu'ils soient conçus spécifiquement pour les fonctions qu'ils

doivent remplir. Notamment, les contraintes citées dans la section

précédente ne peuvent souvent être respectées que si

le système est conçu dès le départ pour pouvoir les

respecter. Il est donc de par sa conception même spécifique.

Le problème qui se pose alors est que, pour chaque

nouvelle fonctionnalité, il faudra concevoir un système

spécifique différent de ceux déjà existants. Le

flot de conception, présenté dans la section II.6 (chapitre II),

et dont le travail de ce mémoire fait partie, s'intéresse

à ce type de système embarqué, et tout

particulièrement aux systèmes sur une puce,

présentés dans le chapitre suivante.

Chapitre II

Conception des logiciels

embarqués

Chapitre II conception des logiciels

embarqués

II.1.Introduction :

La conjonction de l'évolution des technologies de

fabrication des circuits intégrés et de la nature du

marché des systèmes électroniques fait que l'on est

amené à concevoir des circuits de plus en plus complexes

(plusieurs millions) de transistors en un temps de plus en plus court (quelques

mois). Ce phénomène a entraîné une

métamorphose du processus de conception allant de l'idée au

produit.

Durant les dernières décennies, on est

passé de la conception de circuits composés de quelques milliers

de portes à des systèmes structurés et

intégrés comme un réseau sur une même puce. Les

puces modernes peuvent contenir plusieurs processeurs, de la mémoire et

un réseau de communication complexe. Le principe de la conception reste

le même ; il s'agit de générer une réalisation

physique sous forme d'une puce en partant d'une spécification

système. Par contre, les outils mis en oeuvre et l'organisation du

travail durant le processus de conception ont beaucoup évolué.

Partant d'une conception complètement manuelle où l'on dessinait

les masques du circuit à réaliser sur du papier spécial,

on est passé à une conception quasi automatique en partant d'une

description du comportement du circuit sous forme d'un programme décrit

dans un langage de haut niveau.

Le ciblage de logiciel dans le cas des systèmes

embarqués est traité aussi dans ce chapitre. Dans le domaine de

la conception de logiciel, de très nombreux travaux ont

été et sont effectués sur la compilation de descriptions

de haut niveau vers les langages machines (interprétés par les

processeurs). Les habitudes de programmation pour les ordinateurs portes

à croire que la compilation et l'édition de liens sont les seuls

traitements à apporter au logiciel pour pouvoir le faire fonctionner sur

une architecture cible. Le but de ce chapitre est de montrer que dans le cas

des systèmes embarqués, une autre étape est

nécessaire avant la compilation : elle adapte le logiciel à

l'architecture cible spécifique et sera nommée dans ce

mémoire le ciblage logiciel.

II.2.Les systèmes pour puces :

Les prévisions stratégiques d'ITRS annoncent que

70 % des ASIC comporteront au moins un CPU embarqué à partir de

l'année 2005. Ainsi la plupart des ASIC seront des systèmes

mono-puces (SoC pour System on Chip en anglais). Cette tendance semble

non seulement se confirmer mais se renforcer : les systèmes mono-puces

contiendront des réseaux formés de plusieurs processeurs dans le

cas d'applications telles que les terminaux mobiles, les Set top box, les

processeurs de jeux et les processeurs de réseaux. De plus, ces puces

contiendront des éléments non digitaux (par exemple analogique ou

RF) et des mécanismes de communication très sophistiqués.

Etant donné que tous ces systèmes correspondent à des

marchés de masse, ils ont tous été (ou seront)

intégrés sur une seul puce afin de réduire les coûts

de production. Il est prévu que ces systèmes soient les

principaux vecteurs d'orientation de toute l'industrie des semi-conducteurs. Il

est donc crucial de maîtriser la conception de tels systèmes tout

en respectant les contraintes de mise sur le marché et les objectifs de

qualité.

Tous les acteurs dans le domaine des semi-conducteurs

travaillent déjà sur des produits intégrant des

processeurs multiples (CPU, DSP, ASIC, IP, etc.) et des réseaux de

communication complexes (bus hiérarchiques, bus avec protocole TDMA,

connexion point à point, structure en anneau et même

réseaux de communication par paquets) dans des systèmes

monopuces. Certains commencent même à parler de réseaux de

composants monopuces (network on chip). Il s'agit

d'assembler des composants standards pour en faire un

système comme on le fait pour les cartes. Ainsi, le problème

n'est plus tant de concevoir des composants efficaces mais surtout d'obtenir

une architecture qui respecte les contraintes de performances et de

coûts. Pour les composants, le problème devient plutôt de

s'assurer de leur validité avant de les utiliser. Cette évolution

fait que le goulet d'étranglement du processus de conception devient

maintenant la réalisation du réseau de communication des

composants embarqués sur la puce et la validation globale de l'ensemble

du système avant sa réalisation. Ainsi, nous sommes

déjà passés de l'ASIC au SoC et nous sommes en train de

passer au réseau sur puce.

La conception de ces nouveaux systèmes à l'aide

de méthodes classiques conduit à des coûts et des

délais de réalisation inacceptables. En fait, la conception de

ces systèmes induit plusieurs points de cassures qui rendent difficile

la mise en échelle des méthodes de conception existantes. Les

principaux défis sont les suivants :

1. la conception des systèmes multiprocesseurs

monopuces entraînera inévitablement la réutilisation de

composants existants qui n'ont pas été conçu

spécialement pour être assembler sur la même puce. Il sera

donc nécessaire d'utiliser des méthodes d'assemblage de

composants hétérogènes ;

2. le concepteur d'un système contenant des

processeurs programmables doit obligatoirement fournir, en plus du

matériel, une couche logicielle permettant la programmation de haut

niveau du circuit. Il sera donc nécessaire d'aider les concepteurs de

circuits à concevoir les couches logicielles ;

3. l'assemblage de composants

hétérogènes sur une même puce concevoir des

architectures dédiées à des applications

particulières peut nécessiter des schémas de communication

très sophistiqués mettant en oeuvre des parties

matérielles, des parties logicielles et des parties non

numériques telles que les interfaces de composants optiques ou

micromécaniques. La conception de ces interfaces

hétérogènes sera vraisemblablement le principal goulet

d'étranglement du processus de conception des systèmes

multiprocesseurs monopuces ;

4. la complexité des systèmes est telle qu'il

devient quasi impossible de les spécifier/valider manuellement à

des niveaux bas tels que le RTL où il faut donner/valider des

détails au niveau du cycle d'horloge. Des méthodes de

conception/validation basées sur des concepts de plus haut niveau sont

donc nécessaires. Comme pour le logiciel, des outils de synthèse

de haut niveau seront nécessaires pour le matériel. La

vérification des composants synthétisés sera obligatoire

afin de pouvoir en assurer la qualité.

La grande difficulté sera de maîtriser la

complexité lors de la conception de ces réseaux monopuces. Il

s'agira de réussir la conception rapide de système monopuces

multiprocesseurs, et ce, sous de fortes contraintes de qualité et de

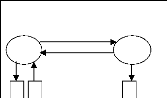

temps de conception. La figure II.1 montre l'architecture d'un système

monopuces. Cette architecture est structurée en couches en vue de

maîtriser la complexité. La partie matérielle est

composée de deux couches :

- la couche basse contient les principaux composants

utilisés par le système. Il s'agit de composants standard tels

que des processeurs (DSP, MCU, IP, mémoires) ;

- la couche de communication matérielle

embarquée sur une puce. Il s'agit des dispositifs nécessaires

à l'interaction complexe allant du simple pont (bridge en

anglais) entre deux processeurs au réseau de communication de paquets.

Bien que le réseau de communication lui-même soit

Chapitre II conception des logiciels embarqués

composé d'élément standard, il est souvent

nécessaire d'ajouter des couches d'adaptation entre le réseau de

communication et les composants de la première couche.

|

Logiciel spécifique à

l'application

|

|

API

|

|

Services du système

d'exploitation

(interruptions, gestion des ressources,

entrées/sorties)

|

|

Pilotes

|

|

Réseau de communication matériel

embarqué

|

|

CPU, IP, mémoires

(DSP, MCU) (ASIC, COTS)

|

Compromis

matériel/logiciel

Logiciel

Matériel

Figure II.1. Architecture

logicielle/matérielle d'un système mono-puce Le

logiciel embarqué est aussi découpé en couches :

- la couche de gestion de ressources permet d'adapter

l'application à l'architecture.

Cette couche fournit les fonctions utilitaires nécessaires

à l'application qu'il est indispensable de personnaliser pour

l'architecture et ce pour des raisons d'efficacité.

Cette couche permet d'isoler l'application de l'architecture.

Cette couche est souvent appelé « système d'exploitation

» (OS). Les applications embarquées utilisent souvent des

structures de données particulières avec des accès non

standard (manipulation de champs de bits ou parcours rapides de tableaux) qui

ne sont généralement pas fournis par les OS standard. D'autre

part, les OS standard sont généralement trop volumineux pour

être embarqués. Il sera souvent nécessaire de

réaliser des OS spécifiques dédiés aux

applications. Le lien avec le matériel se fait via les pilotes

d'entrées/sorties et d'autres contrôleurs de bas niveau, qui

permettent de contrôler les composants de l'architecture. Le code

correspondant à ces pilotes est intimement lié au

matériel. Ces pilotes permettent d'isoler le matériel du reste du

logiciel ;

- le code de l'application.

Cette représentation en couches des systèmes

monopuces permet de séparer la conception des composants logiciels

(application) et matériels (composants existants ou

dédiés) des couches de communication. Elle permet aussi de

définir les différents métiers de conception et la

distribution du travail entre les différentes équipes.

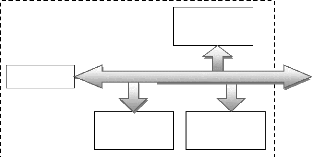

La plupart des méthodes de conception actuelles

essayent de copier le flot de conception des cartes. Ce dernier sépare

la conception en quatre métiers, l'architecture système, la

conception des composants matériels, la conception des composants

logiciels et l'intégration ou la conception système. Les trois

derniers métiers sont montrés dans la figure II.2a. Dans les

schémas traditionnels, le travail de l'architecte consistait à

tailler des composants matériels sur mesure afin de prévoir les

interconnexions de manière efficace et d'obtenir les meilleures

performances. Ainsi tout le matériel est taillé sur mesure, les

composants et le réseau de communication. Le logiciel étant

réalisé à part, le concepteur d'architecture doit juste

fournir une couche mince de logiciel permettant d'accéder aux ressources

matérielles. Le fait que la grande partie des couches de communication

est réalisée par des équipes séparées

(logiciel, matériel) peut entraîner des surcoûts dus aux

précautions et/ou aux sous-

|

Conception

|

Logiciel d'application

|

du API 1

|

logiciel

|

Système d'exploitation sur mesure

|

|

|

Piotes d'entrées/sorties

|

2

|

|

Réseau de communication matériel

|

|

|

intégrateur

|

Conception des composants

|

3

|

|

|

système 1. Concepteur du logiciel

d'application

2. Concepteur des interfaces logicielles/

Matérielles pour système sur puce Concepteur

3. Concepteur de circuit

de circuit

utilisations. La vérification des différentes

parties est aussi réalisée de manière

séparée et chaque équipe utilise des programmes de test

spécifiques.

API

Système d'exploitation standard

Modèle abstrait de l'architecture

Piotes d'entrées/sorties

Réseau de communication

matériel

Modèle des composants matériels

Conception des composants

a) Les métiers pour la conception b) Les

métiers de la conception

des systèmes sur cartes des systèmes sur

puces

Figure II.2 : Les métiers de la conception

système

Ce schéma n'est plus applicable à partir d'un

certain degré de complexité. Ainsi la conception d'architecture

consistera surtout à assembler des composants existants en vue de

respecter des contraintes de performances et de coûts au niveau du

système global et non plus au niveau du seul composant. Ainsi, il

devient crucial de combiner la conception des couches de communication

logicielles et matérielles. Cette évolution permettra la

séparation totale entre la conception des couches de communication et

les composants matériels et logiciels. Une telle séparation est

nécessaire pour introduire un peu de flexibilité et de

modularité dans l'architecture en permettant de charger plus facilement

les modules de base. Ainsi, l'abstraction des interfaces de communication

devient le pivot de la conception des systèmes monopuces.

C'est cette abstraction qui va permettre la conception de

circuits à partir d'un modèle supérieur au niveau RTL

utilisé aujourd'hui. Le fait de pouvoir décrire l'architecture

globale du système et d'abstraire la communication entre les composants

doit permettre de mieux finaliser les interfaces entre les différentes

couches à l'aide de procédure d'interface (API pour

Application Procédure Interface) de haut niveau. Ainsi on

pourra décrire le matériel au niveau comportemental et le

logiciel à un haut niveau ; bien entendu, le but étant de pouvoir

simuler globalement le système à partir de ce modèle

abstrait et de permettre la génération automatique de codes

logiciel et matériel. C'est ce schéma (présenté

figure II.2b) qu'essaient d'atteindre les nouvelles recherches dans le domaine

de la conception système.

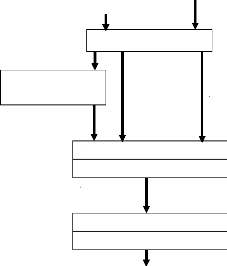

II.3. La conception des systèmes sur puces :

Le flot de conception est généralement

découpé en deux parties, la partie frontale et la partie dorsale

du flot (en anglais ces parties sont appelées front-end et

back-end). La première partie consiste à raffiner les

spécifications initiales pour produire une réalisation de haut

niveau. La partie dorsale du flot réalise les étapes de

conception de bas niveau pour aller à la puce. Le point de

Chapitre II conception des logiciels embarqués

rencontre constitue un contrat (en anglais sign-off)

permettant de sous-traiter la partie dorsale du flot. Au cours des

années, la réalisation de haut niveau faisant l'objet du contrat

à évolué du simple dessin des masques aux modèles

de portes et est en passe d'atteindre le niveau transfert de registre. Il est

prévu que cette évolution continue pour atteindre le niveau

micro-architecture puis le niveau architecture de système contenant

à la fois les parties matérielles (composants et interconnexions)

et les parties logicielles (programmes d'applications et systèmes

d'exploitation).

La partie frontale du flot part d'une spécification

système qui permet de fixer les principales contraintes du produit

à réaliser. Ce modèle sera aussi utilisé pour

l'exploration d'architecture afin de fixer la solution architecturale qui sera

réalisée. Suit alors la conception de cette solution. Cette

étape comporte trois types d'actions ; la conception des composants

logiciels, la conception des composants matériels et la conception des

interfaces logicielles/matérielles.

Le résultat de cette partie est actuellement une

micro-architecture de l'ensemble du système. Les parties

matérielles sont détaillées au niveau transfert de

registre (description au niveau du cycle d'horloge). Dans le cas où le

système contient des parties logicielles exécutées sur un

ou plusieurs processeurs embarqués, elles sont décrites au niveau

de l'instruction (assembleur)

La partie dorsale comprend la conception des parties

matérielles en passant par la conception logique et la conception

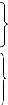

physique. La figure II.3 montre une vue simplifiée de ce flot. Les

rectangles désignent des modèles de description et les ovales des

outils.

Verification, validation (tome!)

Architecture

Code assembleur

Raffinement du Raffinement de la

Synthèse

Logiciel (tome3) communication (tome3)

comportementale

(tome1)

Spécification des parties logicielles

Exploration d'architecture

(tome1)

Produit (niveau physique)

Spécification système

Conception physique

(tome2)

Interconnexion

Conception logique

(tome2)

Micro-architecture

Ports logiques

Spécification des

parties

matérielles

Test (Tome2)

Figure II.3 : le flot de conception

système

Ce flot considère cinq niveaux d'abstraction : le

niveau système, le niveau architecture et le niveau microarchitecture,

le niveau porte et le niveau physique. Au niveau système le circuit est

spécifié au niveau des transactions entre les

éléments de calcul : un ensemble de modules hiérarchiques

et de processus communiquant par protocoles de communication de haut niveau par

l'intermédiaire de canaux abstraits. Un canal peut cacher des protocoles

de communication de haut niveau et des primitives de communication qui

manipulent des types de données abstrait. A ce niveau, les modules

peuvent être décrits en utilisant différents langages et/ou

en utilisant différents niveaux d'abstraction. La cosimulation est

utilisée pour valider la fonctionnalité du système. Ce

modèle peut être utilisé pour explorer l'espace des

solutions architecturales et fixer les grandes lignes de l'architecture. Cette

étape est généralement réalisée à

l'aide d'outils de simulation et d'estimation de performances.

Le deuxième niveau d'abstraction représente une

architecture abstraite qu'on appelle macroarchitecture, ce modèle est

composé d'un ensemble de modules reliés ensemble par des fils

logiques. Chaque module représente un processeur dans l'architecture

finale. Ceci peut être un processeur logiciel (par exemple : un DSP ou un

microcontrôleur exécutant le logiciel), un processeur

matériel (un composant spécifique) ou un module existant

(mémoire globale, périphérique, contrôleur de bus,

etc.). Les fils logiques sont des canaux abstraits qui transfèrent des

types de données fixes (par exemple : nombre entier ou flottant) et

peuvent cacher des protocoles de bas niveau (par exemple : poignée de

main, transfert en mode rafale). Les différents modules peuvent

être décrits en utilisant un ou plusieurs langages. La

cosimulation peut être utilisée pour valider ce découpage

architectural. Cette macroarchitecture peut être utilisée par

différentes équipes pour réaliser les composants

matériels, les composants logiciels et l'intégration des

différents composants. Le résultat de ce flot est une

macroarchitecture du système décrite au niveau transfert de

registre. Ce modèle contient tout les détails de la communication

entre les composants. Les couches de communication logicielles peuvent

comporter un système d'exploitation spécifique (OS). Les couches

de communication matérielles comportent les bus et autres dispositifs

permettent de router les informations entre les composants. Les blocs

matériels sont raffinés au niveau du cycle d'horloge. Finalement,

les blocs existants (souvent appelés IP de l'anglais Intellectual

Property) sont enveloppés dans des interfaces afin de les adapter

aux bus et réseaux de communication utilisés. La connexion entre

les différents blocs matériels est faite par les fils physiques

qui mettent en application les protocoles choisis. Les composants logiciels

communiquent entre eux et avec l'extérieur via des appels système

à l'OS.

Le niveau porte détaille le système au niveau

des délais élémentaires des transferts entre les portes de

base. Finalement, le niveau physique représente les dessins des

masques.

II.4. Les systèmes monopuces :

Les progrès réalisés par les fondeurs de

circuits permettent maintenant d'envisager l'intégration sur une

même puce d'un système embarqué complet. Ces

systèmes monopuces (SoC : system on chip) apportent des changements

importants dans les flots de conception classique.

Dans les systèmes électroniques classiques, les

grandes dimensions des cartes électroniques entraînaient des

problèmes électriques. Ils limitaient notamment la vitesse de

communication. Cela pouvait conduire à des communications lentes entre

des composants potentiellement très rapides. C'était

particulièrement critique pour la communication entre le processeur et

la mémoire : quelle

Chapitre II conception des logiciels embarqués

que soit la vitesse du processeur, il devait aller lire ses

instructions en mémoire. Pour pallier à ces problèmes, il

était nécessaire d'utiliser des caches. L'inconvénient des

caches est dû à la très grande complexité

d'étude de leur système. Ils induisent en plus de gros facteurs

d'indéterminisme. Avec les systèmes monopuces, la communication

reste toujours un goulet d'étranglement, car elle est très

consommatrice de surface, mais avec un facteur bien moindre. En effet le fait

d'avoir sur la même puce l'ensemble du système raccourcit les

chemins de communication et facilite la construction d'architecture s'accordant

aux localités de calcul de l'application. Ces facilités

permettent ainsi souvent de s'affranchir des caches. Les systèmes

monopuces sont aussi moins encombrants et surtout, ils peuvent consommer moins

: en effet les données doivent transiter par des chemins beaucoup moins

longs, l'énergie nécessaire à cette transmission est donc

plus faible.

Les systèmes monopuces apportent aussi des changements

dans les habitudes de conception. Notamment, la frontière entre le

logiciel et le matériel n'est plus aussi nette : en effet avec les

anciens systèmes le matériel était déjà

conçu lorsqu'il fallait concevoir le logiciel. Avec les systèmes

monopuces, les deux doivent être conçus en même temps. Cela

augmente la complexité de la conception, mais cela offre aussi plus de

liberté : chaque partie peut être réalisée en

logiciel, en matériel, ou de manière mixte.

II.5. Conception des systèmes embarqués :

Les systèmes embarqués de première

génération étaient suffisamment simples pour que leur

conception ne requière pas de méthodologie particulière :

quelques essais-erreurs pouvaient suffire pour satisfaire aux contraintes. Avec

la seconde génération, la complexité est devenue trop

importante pour que la conception puisse être menée à bien

sans méthode. Un premier type de flot de conception a donc

été utilisé, inspiré par les flots de conception

pour les systèmes généralistes. Ce flot est

présenté dans la première section. La troisième

génération remet en question ce type de flot, et de nouvelles

méthodes émergent. Elles sont présentées dans la

section suivante.

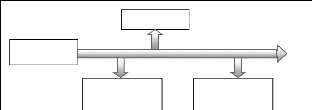

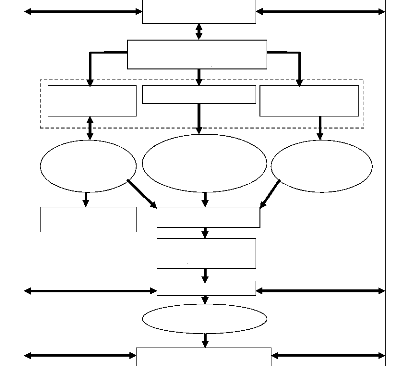

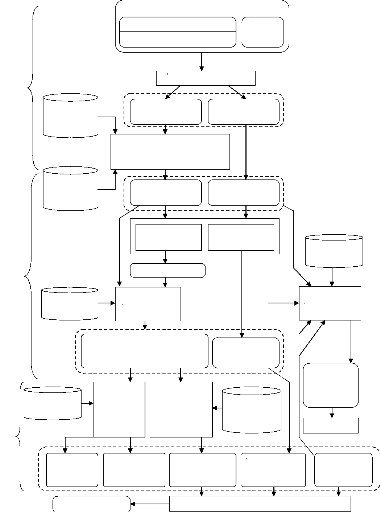

II.5.1. Flots classiques de conception des systèmes

embarqués : II.5.1.1. Le flot :

Le flot classique de conception des systèmes

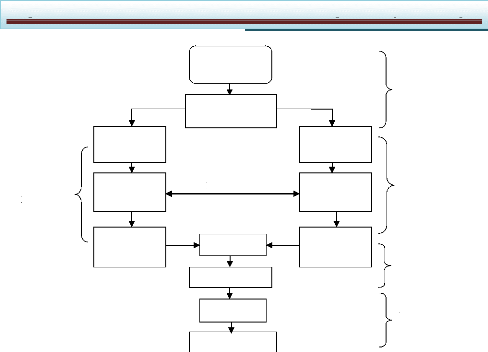

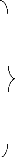

embarqués est représenté sur les figures II.4a et II.4b.

Ce flot part d'une spécification souvent informelle du système.

Il distingue immédiatement les parties logicielles des parties

matérielles. Ces parties sont développées

indépendamment l'une de l'autre par des équipes

différentes. A la fin, une équipe d'intégration assemble

les parties, ce qui pose souvent des problèmes d'incompatibilité.

Cette intégration donne directement un prototype à tester. En cas

d'erreur, il peut être nécessaire de recommencer

complètement le flot.

Dans un tel flot il peut être difficile de

développer complètement le logiciel sans que le matériel

soit défini. C'est pour cela que son développement devait souvent

attendre que la partie matérielle soit décrite pour être

achevé.

Equipe

logicielle

Spécification

logicielle

Conception

logicielle

Prototype

logiciel

Partitionnement

logiciel

/matériel

Prototype final

Compte-rendu

Spécification

générale

Sur le matériel

Information

Intégration

TEST

Spécification

matérielle

Conception

matérielle

Prototype

matériel

Equipe

test

Equipe

intégration

Equipe

matériell

Equipe

système

Figure II.4a : Les flots de conception classiques

pour les systèmes

Equipe

intégration

Equipe

test

Equipe

matérielle

Equipe architecture

Equipe

système

TEST final

Compte-rendu

Equipe

logicielle

Spécification

logicielle

Conception

logicielle

Prototype

logiciel

Partitionnement

synthèse

allocations

Architecture

globale

raffinée/annotée

Intégration

Prototype

Spécification

matérielle

Conception

matérielle

Prototype

matériel

Spécification générale

Définition

de

l'architecture

Architecture globale

Figure II.4b :

Codéveloppement pour les systèmes

embarqués

Chapitre II conception des logiciels embarqués

II.5.1.2. Les limitations du flot classique :

Le flot classique de conception de systèmes

embarqués possède de nombreuses faiblesses qui le rendent

inadapté pour supporter la complexité des systèmes

embarqués de troisième génération.

Tout d'abord, il manque une description globale qui

accompagnerait la conception du système (logiciel et matériel) du

début à la fin. Cette description permettrait à toutes les

équipes de conception de bien connaître l'ensemble du

système, ce qui éviterait de nombreuses erreurs. Il devrait

également être possible d'effectuer des vérifications du

système complet à tous les stades de la conception.

La séparation entre le logiciel et le matériel

est effectuée trop tôt dans le flot de conception : au stade

où elle est effectuée il n'est souvent pas possible de savoir

quelle est la meilleure configuration. A l'inverse, l'intégration des

différentes parties est effectuée trop tard dans le flot : il est

souvent trop tard pour lever les incompatibilités.

Les faiblesses de ce type de flot font que les temps de

développement ne sont plus réalistes pour la conception des

systèmes embarqués actuels.

II.5.2. Flots de conception récents :

Si le flot de conception classique pouvait suffire pour les

première et deuxième générations de systèmes

embarqués, la troisième génération, fortement

hétérogène et multimaître, est trop complexe pour

que les limitations précédemment énoncées soient

acceptable telles que le codéveloppement.

II.5.2.1. Codéveloppement :

Le codéveloppement ou codesing a pour but de

développer conjointement les diverses parties d'un système

hétérogène (logiciel, électronique,

mécanique, etc.). C'est pourquoi une description globale du

système est nécessaire.

Deux approches sont possibles pour cette description : la

première consiste à décrire toutes les parties dans un

langage unique. Ce langage doit alors avoir une sémantique pour chacune

des parties. L'avantage est qu'il est plus simple pour les outils et les

utilisateurs de gérer un langage unique. L'inconvénient est qu'il

est difficile, sinon impossible, de définir un langage qui soit vraiment

adapté à toutes les parties du système. La deuxième

approche consiste à utiliser plusieurs langages, chacun étant

adapté à une partie du système. Un langage de coordination

sert à faire le lien entre toutes les descriptions. L'avantage est que,

cette fois, il est possible d'avoir le langage optimal pour chaque partie.

L'inconvénient est que la gestion de tous ces langages est difficile.

Une partie difficile du codéveloppement est le

découpage entre le logiciel et le matériel. De nombreuses

heuristiques ont été développées, etc. cependant

l'approche manuelle prévaut toujours.

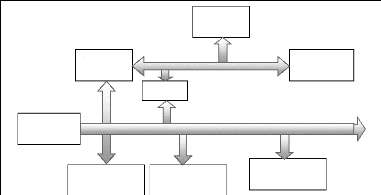

La figure II.4 donne un exemple de flot basé sur le

codévloppement en comparaison avec le flot classique : dans le nouveau

flot, la séparation entre le logiciel et le matériel est

effectuée plus tard, et une nouvelle équipe fait son apparition :

l'équipe d'architecture, qui s'occupe du système global et de la

coordination entre les équipes.

Le codéveloppement repose aussi sur l'utilisation d'une

autre technique permettant la simulation du système aux divers niveaux

d'avancement dans la conception. Ces simulations, appelées

cosimulations, sont décrites dans la section suivante.

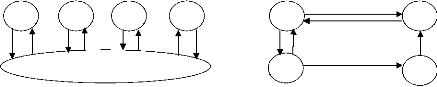

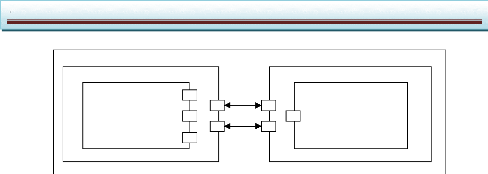

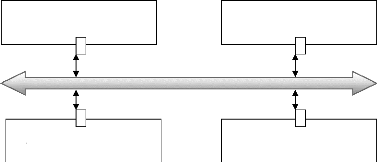

II.5.2.2. Cosimulation :

La cosimulation a pour but de simuler conjointement les

diverses parties d'un système hétérogène. Cela

permet d'effectuer la validation d'un système complet avant le

prototype, mais aussi à divers niveaux d'abstraction.

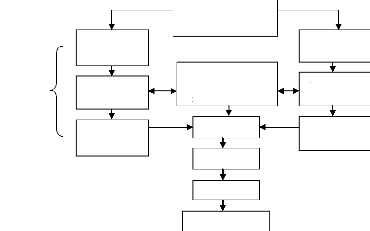

Il existe deux méthodes pour effectuer cette

cosimulation (présentées figure II.5) : la première

consiste à traduire les descriptions des diverses parties dans un unique

langage pour la simulation. Très souvent, il s'agit d'un langage de

programmation tel que le C pour accélérer les simulations. La

difficulté est d'être assuré que la traduction et la

simulation du langage unique ne changent pas la sémantique des

descriptions des diverses parties. La deuxième méthode consiste

à conserver les descriptions spécifiques des diverses parties et

à exécuter en parallèle les divers simulateurs. Un

programme, appelé bus de cosimulation, cette tâche peut

s'avérer difficile à effectuer lorsque les modèles de

simulation sont différents ; de plus les communications entre les

simulateurs peuvent s'avérer coûteuses.

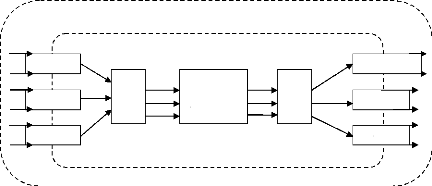

|

Cosimulation avec description

|

Cosimulation multilangage

|

Description

logicielle

Description

matérielle

Description

autre

Description

logicielle

Description

matérielle

Description

autre

Traduction

Simulateur

logiciel

Simulateur

matériel

Simulateur

autre

|

Description

unique

|

|

|

|

|

|

|

|

Simulateur

|

Bus de cosimulation

|

Figure II.5 : Les deux

méthodes de cosimulation

II.6. Exemple de flot de conception pour

systèmes monopuces :

La conception du logiciel est très liée aux

autres étapes et modèles utilisés dans le flot de

conception. Cette section présente un flot typique qui peut servir

d'environnement aux méthodes de conception de logiciel décrites

dans ce travail. Le but est de définir une démarche et un

ensemble d'outils permettant de faciliter la conception des systèmes

monopuces.

L'aide à la conception sera obtenue en élevant

le niveau d'abstraction avec lequel les concepteurs travaillent, et en

automatisant au maximum les passages aux niveaux d'abstraction

inférieurs. Ce flot est centré sur les communications car elles

apparaissent comme étant l'épine dorsale de la conception des

systèmes monopuces.

Chapitre II conception des logiciels embarqués

II.6.1. Présentation générale :

II.6.1.1. Domaine d'application :

Le flot a pour but d'aider à la conception des

systèmes embarqués spécifiques, et notamment les

systèmes sur une puce. Les diverses équipes de conception peuvent

utiliser conjointement cet outil (voir le paragraphe II.5.2). Mais il est tout

particulièrement destiné à l'équipe d'architecture.

L'aide consiste d'une part en l'apport d'une représentation multiniveau

et multilangage de l'architecture globale. Cette représentation sert de

référence pour la conception de toutes les parties du

système et aussi pour sa simulation. D'autre part, elle consiste en

l'apport d'outils d'automatisation de diverses opérations telles que la

génération des interfaces matérielles et logicielles.

Il supporte les architectures hétérogènes

multiprocesseur, multimaîtres et multitâches. Dans ce flot, chaque

processeur dispose d'un système d'exploitation et d'un jeu de

tâches qui lui sont propres. Chaque composant matériel est

encapsulé dans une interface qui adapte ses communications locales aux

communications globales de l'architecture.

II.6.1.2. Les restrictions :

La conception d'un système embarqué complet

commence souvent par une spécification informelle et

générale. Il existe des langages tels que UML qui permettent de

représenter de manière formelle ce type de spécification,

avec un niveau d'abstraction très élevé (le niveau service

du paragraphe II.6.1.3). Le flot proposé n'est pas encore capable

d'intégrer ce type de spécification : il débute plus bas

dans l'abstraction, à un niveau où l'architecture globale est

définie (le niveau fonctionnel du paragraphe II.6.1.3).

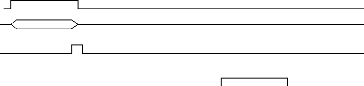

II.6.1.3. Le modèle de représentation de

base :

II.6.1.3.1. La forme intermédiaire utilisée :

Le flot utilise une forme intermédiaire pour

décrire la spécification quels que soient les niveaux

d'abstraction. Cette forme intermédiaire utilise le langage Colif. Ce

langage permet de décrire la structure d'un système, à

plusieurs niveaux d'abstraction, et en mettant l'accent sur les communications.

Les descriptions comportementales sont supposées issues de la

description initiale de l'application.

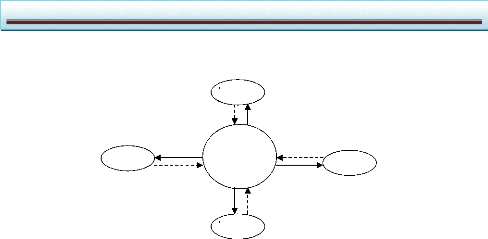

II.6.1.3.2. Les objets de la description :

Quel que soit le niveau d'abstraction, la description est

constituée de modules communicants. Ces modules peuvent

représenter des parties matérielles, des parties logicielles ou

des éléments de mémorisation. Ils communiquent par

l'intermédiaire de ports, au travers de canaux.

Chaque objet (module, port ou canal) est

décomposé en une interface et un contenu. Le contenu de chaque

objet peut être hiérarchique (c'est-à-dire contenir

d'autres objets) ou faire référence à un comportement.

La figure II.6 donne un exemple d'une telle architecture : les

modules, les ports et les canaux sont respectivement nommés M, P et C

lorsqu'ils sont hiérarchiques et m, p et c lorsqu'ils ne le sont pas.

M1

m1

m2

m3

P1

P2

P3

P4

P7

P8

c6

c7

c1

c2

c3

P5

P6

P9

P10

P1

c5

C1

c4 p2

Figure II.6 : La représentation

intermédiaire

|

Niveau

|

service

|

Fonctionnel

|

Macro-

architecture

|

Micro-

architecture

|

|

comportement

|

Objets

concurrents

|

Transactions Partiellement ordonnées

|

Pas de calcul

|

cycles

|

|

communications

|

Requêtes / services

|

Passage de

messages

|

Transmission

de

données

événements

|

Valeurs de bits

|

|

Exemple de

langages

|

CORBA/UML

|

SDL

|

VHDL, systemC

|

VHDL, systemC

|

Tableau II.1 : Exemple de description pour chaque

niveau d'abstraction II.6.1.3.3. Les niveaux d'abstraction utilisés

dans le flot :

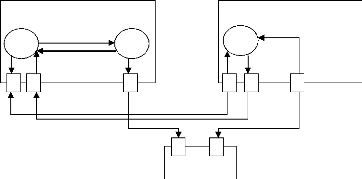

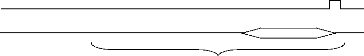

Les systèmes est représenté sur quatre

niveaux d'abstraction différents : le niveau service, le niveau

fonctionnel, le niveau macroarchitecture et le niveau microarchitecture. Le

tableau II.1 compare les caractéristiques de ces différents

niveaux, et la figure II.7 donne un exemple pour chaque niveau. Au niveau

service, les objets peuvent interagir anonymement par le biais de

requêtes et de service. Seules les fonctionnalités sont

définies. Au niveau fonctionnel, les connexions entre les objets sont

définies. Au niveau macroarchitecture, les éléments

d'architecture sont définis : les processeurs, les ASIC,

etc. au niveau microarchitecture, tous les

détails de réalisation sont définis, comme les interfaces

de communications des processeurs ou les systèmes d'exploitation.

Chapitre II conception des logiciels embarqués

Niveau service niveau fonctionnel

R S S

F1 F2 F3

Routeur de requêtes /services

R R S R

F4

S

F1 F1

message

F1 F1

message

message

Niveau macroarchitecture

Processeur 1

F1

Données données

Evénement

Evénement

Evénement

Données

F2

F4

ASIC

Processeur 2

F3

Niveau microarchitecture

Système d'exploitation

Processeur 1

Evénement

Données

F1

F2

Système d'exploitation

Processeur 2

Evénement

F3

Bus adresses bus données bus adresses bus

données

Interface

F4

ASIC

Interface

Figure II.7 : Exemple de description pour chaque

niveau d'abstraction

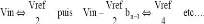

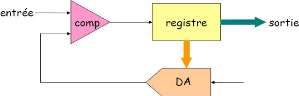

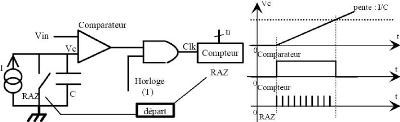

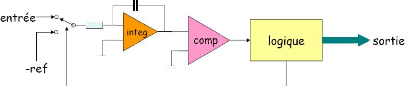

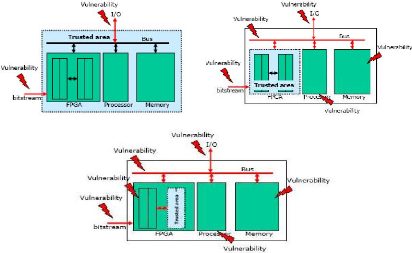

Dans l'exemple de la figure II.7, une application est