2.2.3 Exemple d'architecture de FPGA : la série

Virtex-II Pro de Xilinx (figure10)

Introduite en 2002 et fabriquées en technologie CMOS

1.5V/130nm, la série Virtex-II Pro vise les fortes densités

(jusqu'à 10 millions de portes). Elle intègre en dur de un

à quatre coeurs de processeur RISC IBM PowerPC 405 (jusqu'à

400Mhz) ainsi que des blocs optimisés pour les applications

orientées traitement du signal (blocs de RAMs de 18 Ko et de

multiplieurs 18x18, etc...). Outre la logique programmable, elle comprend ainsi

(Error! Reference source not found.):

- Des entrées/sorties configurables en

entrée, sortie ou bidirectionnel, supportant de nombreux standards

(LDVS, PCI-X, differentiel,...) et interfaçant les pins externes du

circuit et la logique reconfigurable interne.

- Des blocs multiplieurs 18x18 bits cablées et

donc rapides et de faible consommation.

- Des CLBs (Configurables Logics Blocs - Figure

7) qui sont des blocs de ressources programmables permettant

d'implémenter des fonctions combinatoires et séquentielles.

- Des émetteurs/récepteurs série haut

débit (RocketIO) supportant des débits atteignant 3,125 Gb/s

par canal (6,25 Gb/s pour les RocketIO X).

- Des blocs de mémoire selectRAM qui sont des

RAM dual port de 18 kb, chacune programmable en mémoire de 16K X 1 bit

à 512 x 36 bits, et cascadables pour former des blocs mémoires de

taille plus grande.

- Des blocs DCMs (Digital Clock Manager) permettant

la synthèse de fréquences (multiplication et divivion d'horloge),

l'auto-calibration, la compensation des retards pour une parfaite distribution

d'horloge, etc...

1 On peut distinguer les FPGAs par leur type de

mémoire de configuration (fuse, anti-fuse, EEPROM, E2PROM/Flash, SRAM).

Le type détermine la reconfigurabilité du FPGA. Par exemple les

FPGAs à SRAM peuvent facilement être reconfigurés

partiellement et dynamiquement.

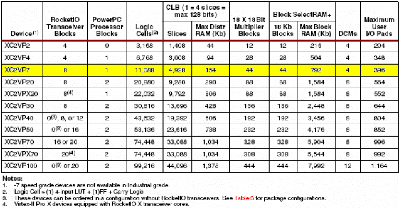

Table 2 : FPGAs de la famille Virtex-II Pro et leurs

principales ressources

(la colonne grisée montre les éléments

du FPGA XVP7 que nous avons utilisée)

2.2.4 Détails de quelques unes des ressources du

Virtex-II Pro

Nous détaillons ci-dessous les caractéristiques qui

permettent de mieux comprendre les règles de reconfiguration du

Virtex-II Pro.

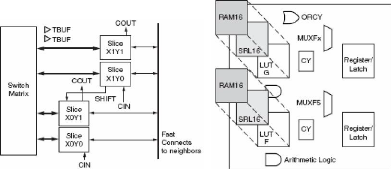

a) Les CLBs (Configurable Logic Blocks - Blocs de

logiques configurables)

Un FPGA Xilinx comprend un certain nombre de colonnes de

CLBs. Chaque CLB comprend 4 Slices identiques et 2 buffers tri-states (TBUF,

Figure 7) . Chaque colonne de CLB comprend 2 colonnes de Slices.

Chaque CLB est relié à une matrice d'interconnexion (switch

matrix) pour accéder à la matrice générale de

routage. Les Slices d'un même CLB sont reliés entre eux et aux

CLBs voisins par des interconnexions directes et rapides (fast connects to

neighbors, Figure 7).

b) Les SLICES (Figure

78) Chaque Slice contient :

- Deux générateurs de fonction (F & G); ce

sont des LUTs (Look-Up-Table) pouvant implémenter soit une fonction

logique à 4 entrées, soit une mémoire SelectRAM 16 bits

(dans ce cas on parle de distributed selectRam) , ou encore un

registre à décalage 16 bits.

- Deux éléments de stockage (Register/Latch) qui

servent de registres D flip-flop de sortie.

- Deux multiplexeurs MUXFX qui combinés aux

générateurs de fonction permettent de générer des

fonctions logiques de plus de 4 entrées.

- Des portes logiques qui facilitent l'implémentation de

la logique arithmétique ( des XORs pour additionneurs, des ORs pour les

sommes de produit et des ANDs pour les multiplieurs).

- Des chaînes de propagation rapide de retenue (CY).

Figure 7 : Structure interne d'un CLB Figure 8 : Structure

interne d'un Slice

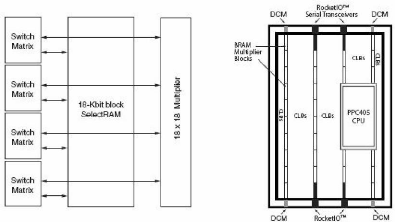

Figure 9 : Bloc multiplieur et SelectRam Figure 10 : Vue

générale du

Virtex-II Pro XVP7

c) Les blocs multiplieurs 18 x 18 bits

(Figure 910)

Ils réalisent des multiplications en complement

à 2 (signes), et peuvent être associés à de blocs

memoires SelectRam 18 Kb pour former des modules MAC (Multiplier-Accumulator)

très utiles en traitement numérique du signal (filtres FIR et

IIF). Cables en dur, ils sont optimisés en vitesse et en consommation.

Un virtex-II pro peut contenir jusqu'a 444 blocs multiplieurs de ce type, et

autant de blocs SelectRam (Error! Reference source not

found.).

Toutes ces ressources permettent également au Slice de

combiner avec des Slices voisins pour implémenter des fonctions plus

complexes.

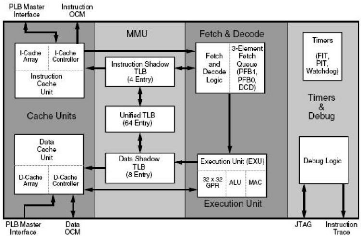

d) Le processeur PowerPC 405

Le PowerPC 405 est un processeur RISC1 de 32 bits

d'architecure Harvard1. Il est optimise pour de hautes performances

(jusqu'à 400Mhz pour certains) et des basses consommations (0.9mW/MHz).

Il est intégré dans le FPGA Virtex-II Pro comme le montre la

Figure 9 10.

Figure 11 : Architecture générale du processeur

PowerPC 405 Il possède essentiellement:

- Une MMU (memory management unit) qui peut faciliter la misen

en oeuvre d'un systeme de fichier, solution envisageable dans notre cas pour

stocker les configurations en mémoire embarquée sous forme de

fichier.

- Deux interfaces mémoires (Figure 11) ;

l'interface OCM (On-Chip-Memory) subdivisée en deux blocs ; l'un pour

les données et l'autre pour les instructions et l'interface PLB.

- Une interface JTAG permettant le debugage (en plus de trois

autres modes de debogage supportés).

- Un pipeline de 5 étages

- Des caches de données et d'instruction

séparées et de 16 Ko chaque. - 3 Timers programmables.

1 Reduced Instruction Set Computer ; concept consistant

à réduire le jeu d'instruction des processeur, et parti du

constat suivant lequel dans 80% des cas un processeur n'utilisait que 20% de

son jeu d'instruction (essentiellement des Load/Sore)

- Une unité de division/multiplication.

En outre ce processeur implémenté en dur occupe

2% de la surface totale d'un FPGA Virtex-II Pro XVP50 par exemple

(Error! Reference source not found.). Mais il n'a pas

d'unité arithmétique flottante.

Le processeur est connecté au bus PLB (Processor Local

Bus) directement, et a un second bus (OPB pour On-chip Peripheral Bus)

via un pont entre les deux bus.

|