II-4 PRINCIPE DE FONCTIONNEMENT

Lorsque toutes les sécurités ont

été vérifiées par l'automate, les cabines quittent

les stations à une vitesse voisine de 0,5 m/s pendant quelques

mètres pour atteindre progressivement la vitesse nominale de 12,5

m/s.

A l'arrivée, à proximité de la gare, les

cabines ralentissent une première fois, ensuite les cabines ralentissent

de nouveau, puis s'arrêtent aux quais de débarquement respectifs.

Le frein de service est actionné et les portes peuvent s'ouvrir.

Il est impératif d`arrêter les cabines de

manière imminente et à n'importe quelle position, pour des

raisons telles que `vents forts', `incohérence des informations issues

des capteurs de vitesse et de position des cabines'.Aussi, au

redémarrage, la machine motrice devra fournir le couple

nécessaire pour déplacer les cabines. Ce couple peut atteindre

des valeurs importantes, largement supérieures au couple nominal.

II-5 LES MODES D'EXPLOITATION

Afin de répondre en toute sécurité

à toutes les circonstances qui peuvent se présenter en cours

d'exploitation, l'opérateur dispose de quatre modes de marche :

· mode de marche automatique : Tout le cycle de

fonctionnement est pris en charge par les automates.

· mode de marche manuel : Le préposé

assure la totalité des opérations. La vitesse en

différents points du parcours est comparée à celle

définie pour la marche en automatique. S'il y a discordance, le

système est arrêté par action sur le Bpa.

· mode de marche exceptionnel : Ce mode de marche est

utilisé dans le cas de pannes d'automatisme importantes. La plupart des

sécurités sont inhibées. La vitesse est limitée

à 1 m/s.

· mode de marche secouru : L'entraînement est

assuré par un générateur électrique (Groupe

électrogène).

L'automate principal prend en charge :

· La commande des portes.

· L'élaboration des ordres de mouvement.

· L'élaboration des consignes de vitesse pour le

variateur.

· La gestion des défauts de fonctionnement.

Projet de fin de cycle rédigé par MOELET GOMA

Jean Hermann Page 39

Projet de fin de cycle rédigé par MOELET GOMA Jean

Hermann Page 40

Étude et réalisation d'un moyen de

transport par câble aérien commandé par un API

adaptable

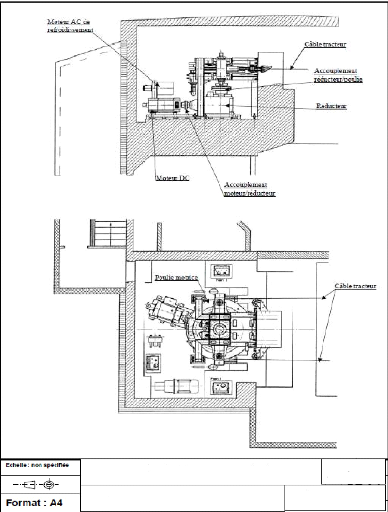

SALLE DES MACHINES

PROJET DE FIN DE CYCLE

MÉMOIRE

ANNÉE 2011

Fig.16 Vue d'une salle des machines

2011

CHAPITRE III :

ÉTUDE PRATIQUE

(Réalisation d'un

micro-téléphérique)

Étude et réalisation d'un moyen de

transport par câble aérien commandé par un API

adaptable

(Téléphérique)

Projet de fin de cycle rédigé par MOELET GOMA

Jean Hermann Page 41

Projet de fin de cycle rédigé par MOELET GOMA Jean

Hermann

Page 42

Étude et réalisation d'un moyen de

transport par câble aérien commandé par un API

adaptable

Le PFE porte sur la conception d'un API adaptable constituant

notre centrale Informatique dont l'élément mère est le

microcontrôleur ATméga 168 D'Atmel qui doit gérer

tout notre système. Pour ce faire nous sommes donc emmené

à construire un environnement dans lequel le microcontrôleur sera

en mesure de recevoir des informations de natures différentes, de les

traiter, et de les restituer aux différents types d'actionneurs.

Le microcontrôleur est un circuit intégré

qui regroupe sur une même puce tous les éléments d'une

structure à base de microprocesseur.

Le microcontrôleur ATméga ou ATtiny font partie

de la grande famille de circuit AVR. Le catalogue d'Atmel ne contient que des

microcontrôleurs à architecture RISC. Il existe en effet toute une

gamme de circuits, compatible des célèbres 8051 d'Intel.

Par contre les circuits RISC d'Atmel sont tous regroupés sous le vocable

de microcontrôleurs AVR, divisés en deux groupes bien distincts au

moins en termes de performances. Celui des microcontrôleurs 8

bits et celui des microcontrôleurs 32 bits. Ils

présentent des représentations physiques diverses. Avec

l'évolution de la technologie visant à l'amélioration des

microcontrôleurs, plusieurs furent replacés par de nouveaux

microcontrôleurs détenant une technologie de pointe (Cas de l'AT90

replac é par ATméga et ATtiny).

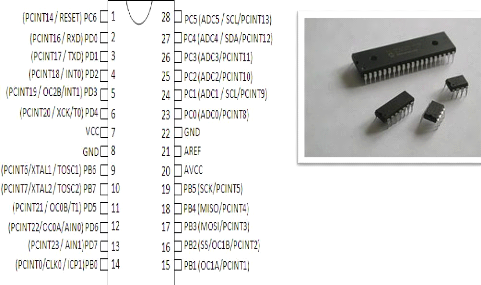

C'est donc dans le but d'utiliser le microcontrôleur

performant que nous avions choisis l'ATméga 168 beaucoup

usité de nos jours. Sa représentation physique s'apparente

à celle de l'ATméga 88 et comporte au total 28

broches.

Img. 1 Microcontrôleur ATméga et

ATtiny

Fig.18 Description des différentes

Broches

Projet de fin de cycle rédigé par MOELET

GOMA Jean Hermann Page 43

Étude et réalisation d'un moyen de

transport par câble aérien commandé par un API

adaptable

> Port B (PB7 à PB0) le Port B est un

port d'entrée-sortie à 8 bits bidirectionnel avec des

résistances internes de tirage (choisi pour chaque bit). Il sert aussi

comme oscillateur pour le Timer/Compteur2.

> Port C (PC6 à PC0) le Port C est

un port d'entrée-sortie à 7 bits bidirectionnel avec des

résistances internes de tirage (choisi pour chaque bit). Il sert aussi

de convertisseur analogique numérique.

> RESET(PC6) déclenché par

un front descendant maintenue plus de 50 ns il produira le Reset du

microcontrôleur.

> Port D (PD7à PD0) le Port D est

un port d'entrée-sortie à 8 bites bidirectionnel avec des

résistances internes de tirage (choisi pour chaque bit). Il sert aussi

d'USART et d'entrées pour les interruptions externes.

> XTAL1 Entrée de l'oscillateur

externe ou libre pour l'horloge interne.

> XTAL2 Production de l'amplificateur

d'oscillateur.

> AVCC est une broche de tension

d'alimentation pour le Convertisseur A/D qui doit être connectée

à VCC via un filtre passe-bas pour éviter les parasites.

> AREF est l'entrée de

référence analogue pour le Convertisseur A/D avec une tension

dans la gamme de 2 V à AVCC avec filtre passe-bas.

> GND (22) masse analogique. Si la masse

analogique est séparée de la masse générale,

brancher cette broche sur la masse analogiques, sinon, connecter cette broche

à la masse générale GND.

> VCC broches d'alimentation du

microcontrôleur (+3 à +5V).

> GND masse de l'alimentation.

Il se présente sous la forme d'un circuit

intégré réunissant tous les éléments d'une

structure à base de microprocesseur. Voici généralement ce

que l'on trouve à l'intérieur d'un tel composant :

> Un microprocesseur (C.P.U.) exécutant

séquentiellement les instructions stockées dans la mémoire

programme, il est généralement composé de :

· Un ou plusieurs registres accumulateurs contenant

temporairement les opérandes et les résultats des

opérations.

· Des registres auxiliaires permettant de relayer les

accumulateurs.

· Des registres d'index pour le mode d'adressage

indirect.

· Un compteur programme pointant l'adresse de la prochaine

instruction à exécuter.

· Une ALU permettant d'effectuer des opérations

entre l'accumulateur et l'opérande.

· Un registre code condition indiquant certaines

particularités en ce qui concerne le résultat de la

dernière opération (retenu, zéro, interruption).Toutes

fois il est important de signaler qu'il existe deux catégories de

microprocesseur : les CISC et les RISC.

> De la mémoire de donnée (RAM et EEPROM)

qui permet de mémoriser temporairement les données

générées par le microprocesseur pendant les

différentes phases du traitement numérique (résultats

d'opérations, etc...).

> De la mémoire programme (ROM, OTPROM, UVPROM ou

EEPROM) qui est uniquement accessible en lecture (dite mémoire morte).Sa

programmation nécessite une procédure particulière et un

matériel adéquat.

> Des interfaces parallèles pour la connexion des

entrées / sorties reparties sur plusieurs ports (maximum 8 bits),

permettent de prendre en compte des états logiques appliqués en

entrée ou de

Projet de fin de cycle rédigé par MOELET GOMA Jean

Hermann Page 44

Étude et réalisation d'un moyen de

transport par câble aérien commandé par un API

adaptable

gérer des signaux binaires en sortie. Les broches de

ces ports peuvent donc être configurées en entrée ou en

sortie, avec différentes options (résistances de rappel, sorties

collecteurs ouverts, interruption...). La configuration ainsi que l'état

logique de ces broches est obtenue par des opérations d'écriture

ou de lecture dans différents registres associés à chaque

port. On trouve généralement:

· Un registre de direction pour une configuration en

entrée ou en sortie,

· Un registre de donnée recopiant les états

logiques de chaque broche de port,

· Un registre d'option permettant plusieurs configurations

en entrée ou en sortie.

> Des interfaces séries (synchrone ou asynchrone)

pour le dialogue avec d'autres unités. Les données

envoyées ou reçues se présentes sous la forme d'une

succession temporelle (sur un seul bit) de valeurs binaires images d'un mot.

> Des timers pour générer ou mesurer des signaux

avec une grande précision temporelle.

> Des convertisseurs analogique / numérique pour le

traitement de signaux analogiques.

> Du chien de garde, qui empêche le plantage du

microcontrôleur tout en s'assurant qu'il n'y ait pas d'exécution

prolongé d'une même suite d'instruction.

La majorité des microprocesseurs et

microcontrôleurs utilisent actuellement une architecture interne dite

VON NEUMANN, c'est-à-dire une architecture commune

à celle que l'on rencontre habituellement dans les micro-ordinateurs.

La mémoire, appelée improprement de programme,

contient en fait des instructions et des données placées à

la suite les unes des autres et on ne dispose que d'un bus, appelé bus

de données, pour véhiculer tour à tour les codes des

instructions et les données qui leur sont associées. Si cette

architecture donne toute satisfaction comme nous en avons la preuve

éclatante chaque jour, elle pose quelques problèmes dès

que l'on veut faire fonctionner l'ensemble rapidement. En effet,

l'exécution d'une seule instruction nécessite plusieurs

échanges de données sur le seul et unique bus dévolu

à cet usage puisqu'il faut tout d'abord aller chercher le code de

l'instruction.

Il est alors préférable de faire appel à

une architecture dite HARVARD dans laquelle les instructions et les

données sont clairement différenciées. Ces

dernières sont contenues dans des mémoires différentes et

sont véhiculées sur des bus indépendants.

Bien sûr, vu de l'utilisation, cela ne change rien et

les circuits de ce type s'utilisent exactement comme les autres. Par contre,

les résultats obtenus, en termes de vitesse d'exécution de

programmes peuvent être impressionnants. En effet, l'exécution

d'une instruction ne fait plus appel qu'à un seul cycle machine puisque

l'on peut simultanément, grâce aux deux bus et aux deux

mémoires indépendants, rechercher le code de l'instruction.

Rompant avec une tradition bien établie, les microcontrôleurs AVR

d'Atmel utilisent une architecture HARVARD mais ce n'est pas tout. Ils font

également appel à une architecture de type RISC

qui, comme on le lit un peu trop souvent, ne se résume pas

simplement à disposer d'un jeu d'instructions réduits ; ce qui,

paradoxalement, n'est d'ailleurs pas le cas des circuits AVR.

Projet de fin de cycle rédigé par MOELET GOMA Jean

Hermann Page 45

Étude et réalisation d'un moyen de

transport par câble aérien commandé par un API

adaptable

Unité

Centrale Bus de données

Mémoire de programme contenant instructions et

données

Fig.19 Architecture Von Neumann

Mémoire de

données

Unité

Bus de données Centrale Bus

d'instructions

Mémoire de programme ne contenant que des

instructions

Fig.20 Architecture de Harvard

L'architecture RISC (ce qui veut dire circuit à jeu

d'instructions réduits) présente un avantage considérable

sur les microcontrôleurs. Un vrai circuit de type RISC doit

présenter un certain nombre de particularités propres à

accroître sa vitesse de fonctionnement.

Et tous microcontrôleurs conçus par cette

architecture utilisent des instructions codées sur un seul mot. Cela

présente deux avantages. Le premier est que tous les emplacements de la

mémoire de programme contiennent une instruction, le second est qu'un

seul cycle machine suffit pour lire le code complet d'une instruction,

d'où un gain en vitesse d'exécution. Les circuits RISC utilisent

en suite une structure PIPE LINE qui leur permet

d'exécuter une instruction tout en recherchant la suivante en

mémoire d'où, l'accroissement de la vitesse. Ils exécutent

toutes leurs instructions en un seul cycle machine ce qui est dû en

grande partie au codage de l'instruction sur un seul mot. L'Unité

Arithmétique et Logique, appelé encore « ALU », dispose

en effet en une seule fois de toutes les informations nécessaires

à l'exécution de l'instruction. Les instructions d'un circuit de

type RISC ont une structure aussi Orthogonale que possible,

c'est-à-dire que toutes les instructions peuvent être

exécutées sur tous les registres avec tous les modes d'adressage.

Cela signifie que le travail du programmeur, et donc le nôtre, car il

n'est plus nécessaire de retenir une multitude de cas particuliers

d'instructions qui ne fonctionnent que dans un mode ou dans l'autre.

Nota: Les microcontrôleurs AVR sont

réalisés en technologie CMOS haute vitesse, ce qui leur

confère tout à la fois une faible consommation, une vitesse de

fonctionnement importante et un haut niveau d'intégration. Ils adoptent

tous une véritable architecture RISC de type HARVARD et toutes les

instructions s'exécutent en seul cycle machine. De ce fait leur

puissance exprimée en MIPS (million d'instructions par seconde) est

égale à leur fréquence d'horloge.

Projet de fin de cycle rédigé par MOELET GOMA Jean

Hermann

Page 46

Étude et réalisation d'un moyen de

transport par câble aérien commandé par un API

adaptable

I- ÉTUDE LOGICIELLE

Les logiciels mis en oeuvre au pour notre réalisation

sont :

> AVR Studio 4 : la

simulation du programme de notre maquette

> KiCad : pour la saisie du schéma

de montage et le traçage du typon

|