5.1 PORT A :

Le PORTA est un port de six bits donc six

entrées/sorties numérotées de RA0 à RA5 qui peuvent

être utilisées comme des entrées pour le : (Convertisseur

Analogique Numérique, le TIMER0, dans ce cas la pin RA4 sera

utilisé comme entrée pour configurer TOCKI est de type drain

ouvert). Les registres associés avec le port A sont :

|

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

|

PORTA

|

x

|

X

|

RA5

|

RA4

|

RA3

|

RA2

|

RA1

|

RA0

|

|

TRISA

|

Registre de Direction du PORTA

|

|

ADCON1

|

ADFM

|

X

|

x

|

x

|

PCFG3

|

PCFG2

|

PCFG1

|

PCFG0

|

y' Registre TRISA :

TRISA=1 : les lignes du PORTA sont configurées en ENTREES,

et le driver de sortie est placé en haute impédance.

TRISA=0 : les lignes du port sont configurées en

SORTIES.

y' Registre ADCON1 :

Ce registre sera étudié dans le chapitre

concernant le CAN. On retiendra seulement que pour configurer les 5 bits du

Port A en entrées sorties digitales, il faut positionner les 4 bits PCFG

à 0110.

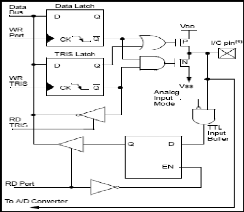

Figure I.8 : Schéma interne d'une ligne

d'entrée sortie du PORTA

5.2 PORT B :

C'est un port bidirectionnel de 8 bits (RB0 à RB7). Ses

registres associés sont :

|

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

|

PORTB

|

RB7

|

RB6

|

RB5

|

RB4

|

RB3

|

RB2

|

RB1

|

RB0

|

|

TRISB

|

Registre de Direction Du PORTB

|

|

OPTION_REG

|

RBPU

|

TOCS

|

INTEDG

|

TOSE

|

PSA

|

PS2

|

PS1

|

PS0

|

y' Registre TRISB :

Le PORTB est configuré en entré si TRISB est mis

à 1 et lorsque ce dernier est mis 0 le PORTB est en sortie.

En mode entrée chaque broche du PORTB doit être

maintenue à un niveau haut par

l'intermédiaire de résistances de 10 k pour ne pas

déclencher d'interruptions imprévues qui peut être

activé ou désactivé par la mise à 1 ou a 0 du

7èmè bit du registre OPTION.

Au reset, le tirage est désactivé. Il est inactif

quand le port est configuré en sortie.

En entrée, les broches RB4 à RB7 peuvent

déclencher l'interruption. On parlera là- dessus dans le

paragraphe réservé aux interruptions.

y' Registre OPTION :

Ce registre en lecture écriture permet de configurer les

prédiviseurs du Timer et du Watchdog, la source du Timer, le front des

interruptions et le choix du Pull up sur le Port B.

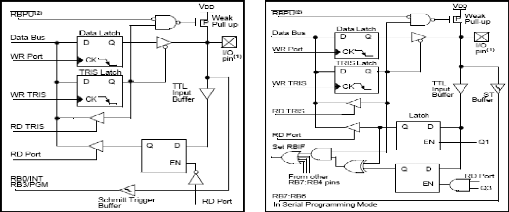

Figure I.9 : Schéma interne d'une ligne

d'entrée sortie du PORTB

Pins (RB3 -

RB0) Pins (RB7-RB4)

5.3 PORT C :

Il s'agit d'un PORT de 8 bits bidirectionnels. Il est

partagé avec le module de transmission synchrone I2C et l'USART. La

configuration de direction se fait à l'aide du registre TRISC.

Les registres associés sont :

|

Nom

|

Bit7

|

Bit6

|

Bit5

|

Bit4

|

Bit3

|

Bit2

|

Bit1

|

Bit0

|

|

PORTC

|

RC7

|

RC6

|

RC5

|

RC4

|

RC3

|

R

|

RC1

|

RC0

|

|

TRISC

|

Registre de Direction du PORTC

|

V' Registre TRISC:

La mise à 1 de ce registre configure la broche

correspondante en entrée, et inversement.

Au reset toutes les broches sont configurées en

entrée. Toutes les broches du port C peuvent être utilisées

soit comme E/S normales soit comme broches d'accès à

différents modules comme le timer1, les modules de comparaison et de

capture CCP1/2, le timer 2, le port I2C ou le port série, ceci sera

précisé au moment de l'étude de chacun de ces

périphériques.

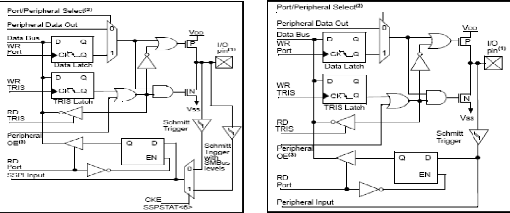

Figure I.10 : Schéma interne d'une ligne

d'entrée sortie du PORTC

Pins (RC7-RC5, R-RC0) Pins

(RC3-RC4)

|